PHASE COMPARISON RELAY

**TYPES**

SLD42D1 SLD42D2

POWER SYSTEMS MANAGEMENT DEPARTMENT

GENERAL ( ELECTRIC

PHILADELPHIA, PA.

# CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                             | PAGE                                                                                           | <u>FIGURES</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDENDUM                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| APPLICATION  GENERAL  LOAD CURRENT  SHUNT CAPACITANCE  SERIES CAPACITANCE  INFORMATION REQUIRED FOR SETTING CALCULATION  CALCULATION OF SETTINGS  PICKUP SETTINGS OF FDH AND FDL  SELECTION OF K FACTOR  SETTING OF FDM  PICKUP SETTING OF G4  SAMPLE CALCULATIONS  SELECTION OF K FACTOR  SETTING OF FDM  DESCRIPTION  FUNCTIONS  NETWORK UNIT  LOGIC UNIT  ASSOCIATED EQUIPMENT  RATINGS  TEMPERATURE  ELECTRICAL  BURDEN | 3A<br>3A<br>4A<br>5A<br>5A<br>6A<br>7A<br>8A<br>1<br>1<br>1<br>1<br>2<br>2<br>2<br>2<br>3<br>3 | I INTERNAL CONNECTIONS - NETWORK UNIT II INTERNAL CONNECTIONS - LOGIC & TRIP UNIT 1 SLD42D PHOTOGRAPH 2 NETWORK UNIT OUTLINE 3 NETWORK UNIT COMPONENT LOCATIONS 4 LOGIC UNIT COMPONENT LOCATIONS 6 TEST RECEPTACLE OUTLINE 7 EXTERNAL CONNEC 8 OVERALL LOGIC 9 LOGIC SYMBOL LEGEND 10 OPERATING PRINCIPLE 11 NETWORK UNIT INTERNAL CONN. 12 NEG. SEQUENCE NETWORK 13 NETWORK RESPONSE DIAGRAM 14 LOGIC UNIT INTERNAL CONN. 15 IKL & IKF ANGLE CURVE 16 I1F & 12 IN DOG FAULTS 17 SAMPLE SYSTEM DATA 18 K SELECTION CURVES 19 KEYING PHASOR DIAG. (DG) 20 KEYING PHASOR DIAG. (DG) 21 NETWORK BALANCE TEST CONN. 22 CT PHASING & POLARITY TEST 23 LEVEL DETECTOR TEST CONN. |

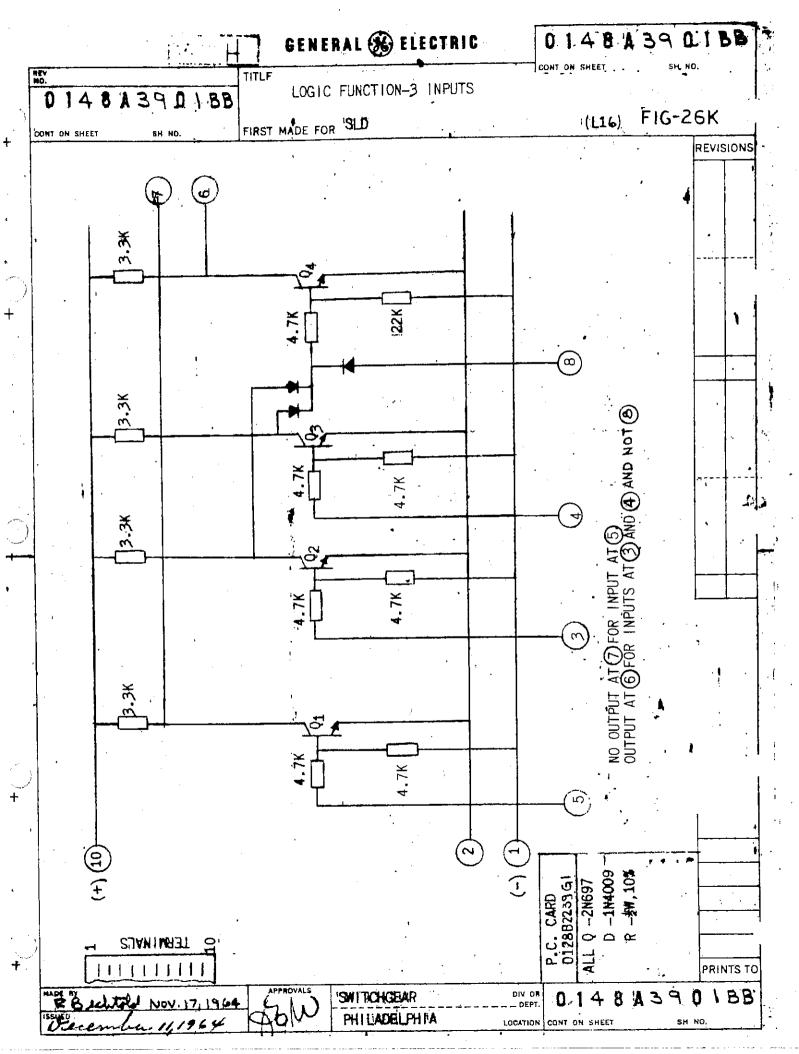

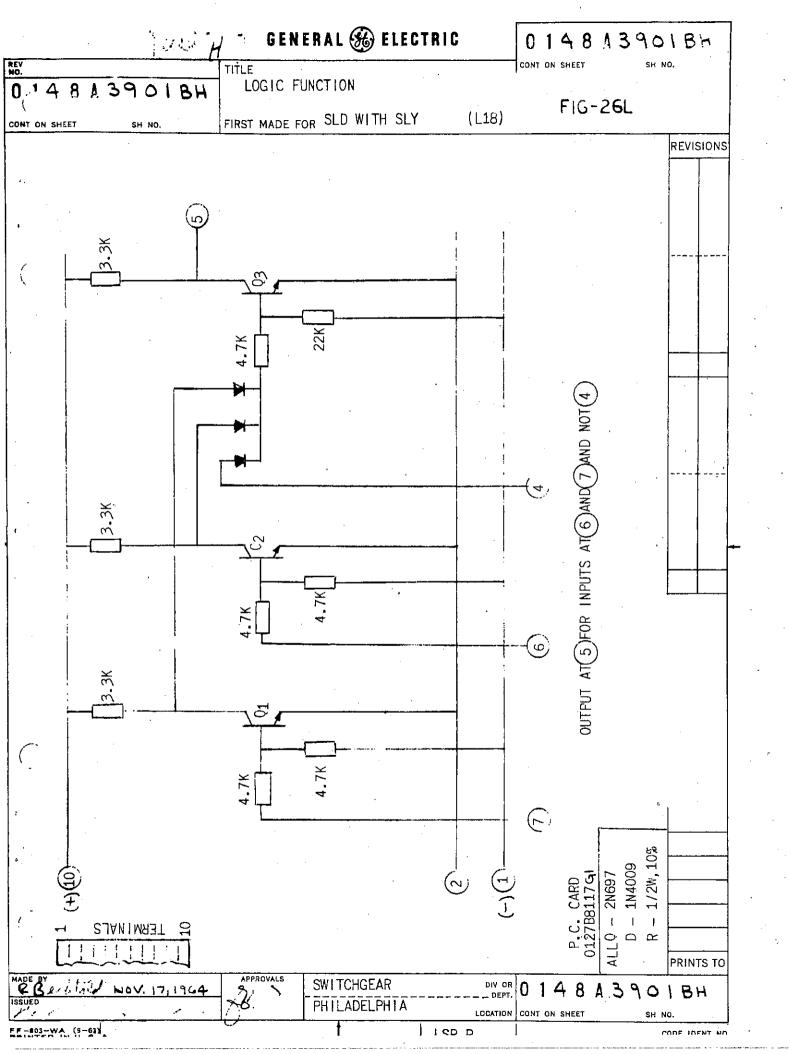

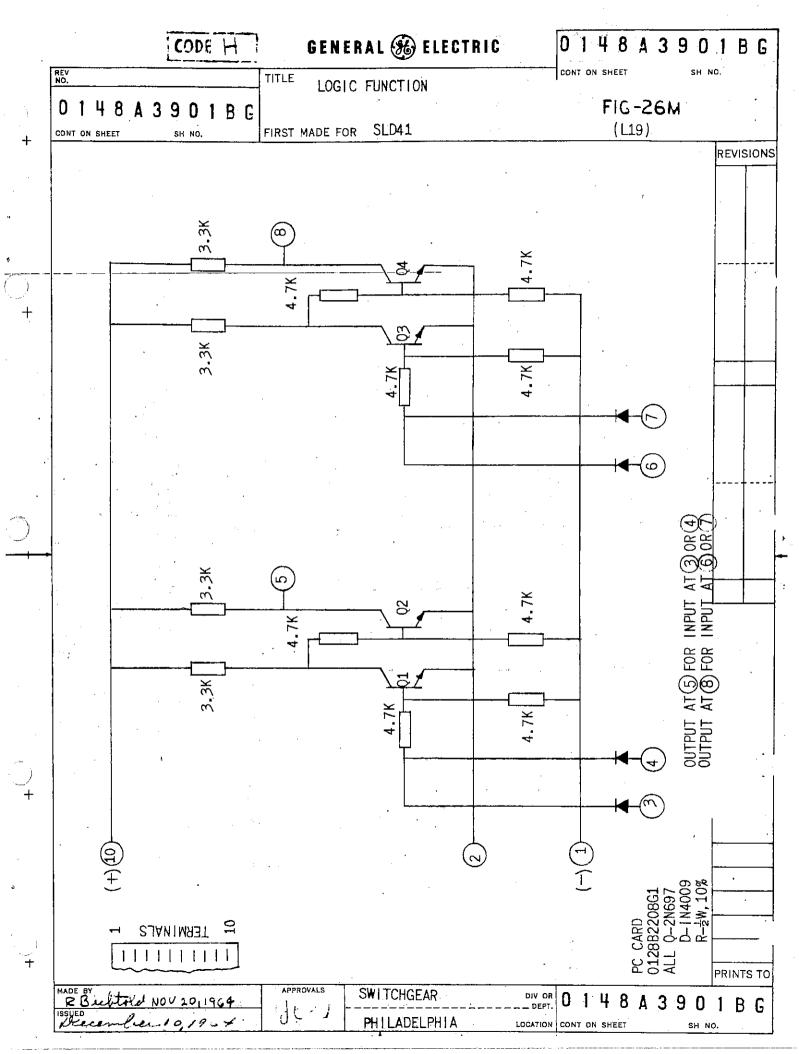

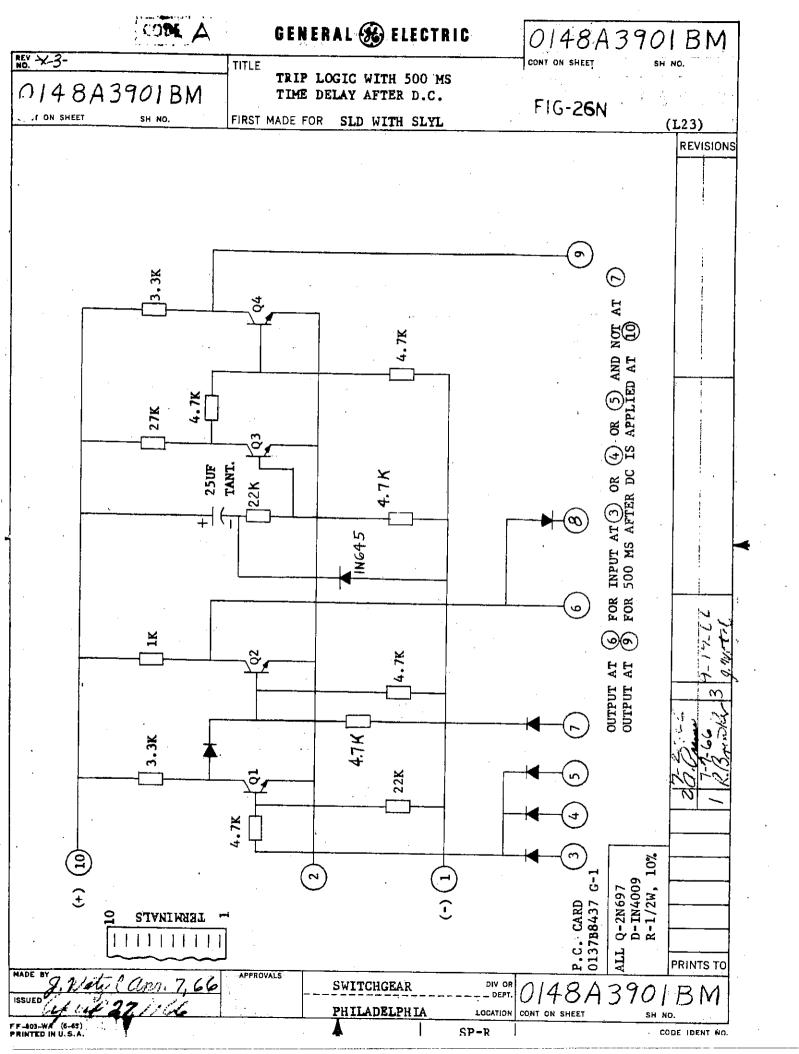

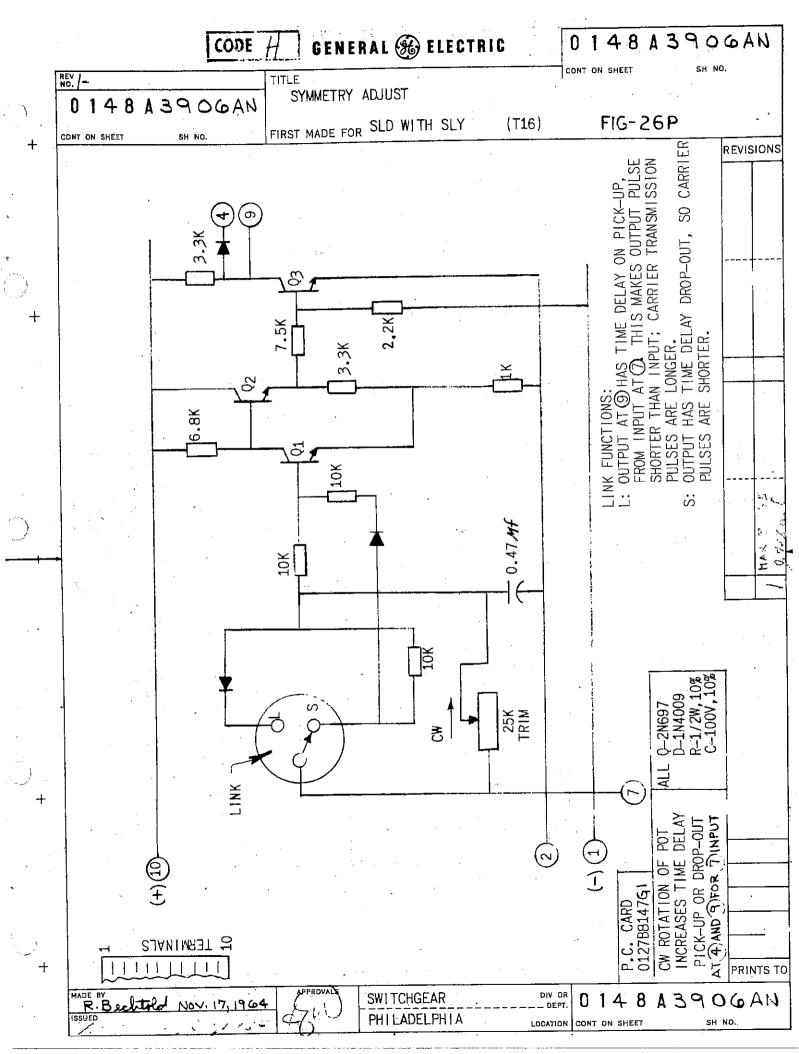

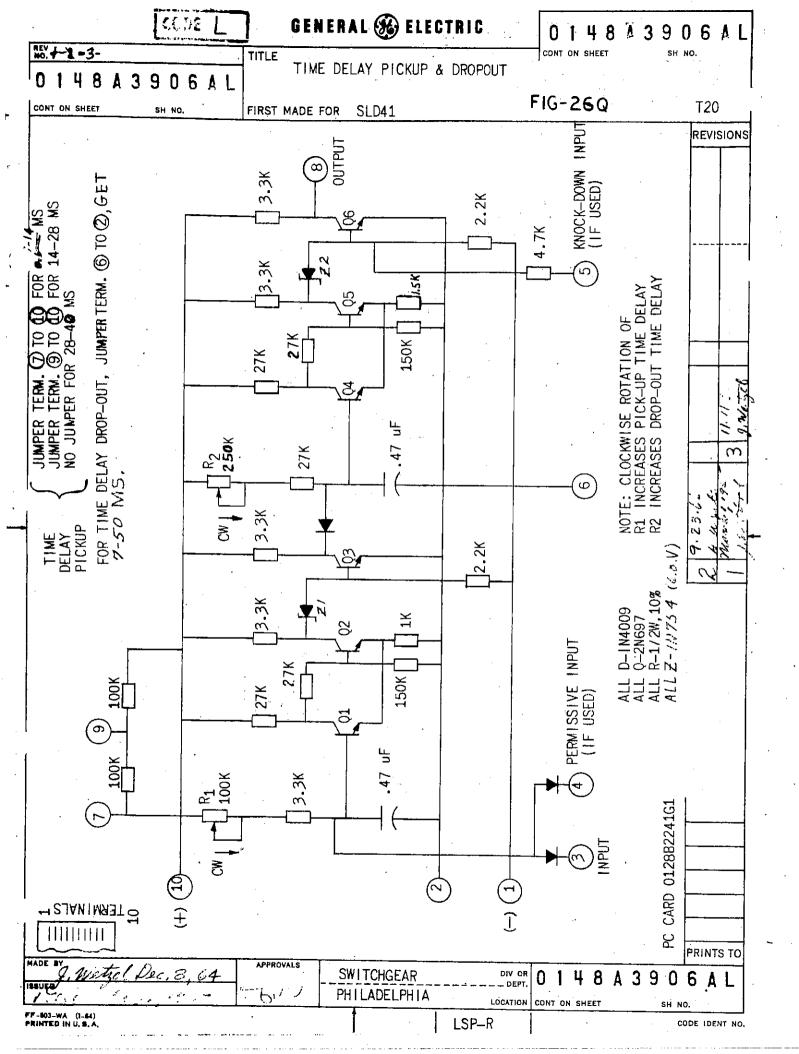

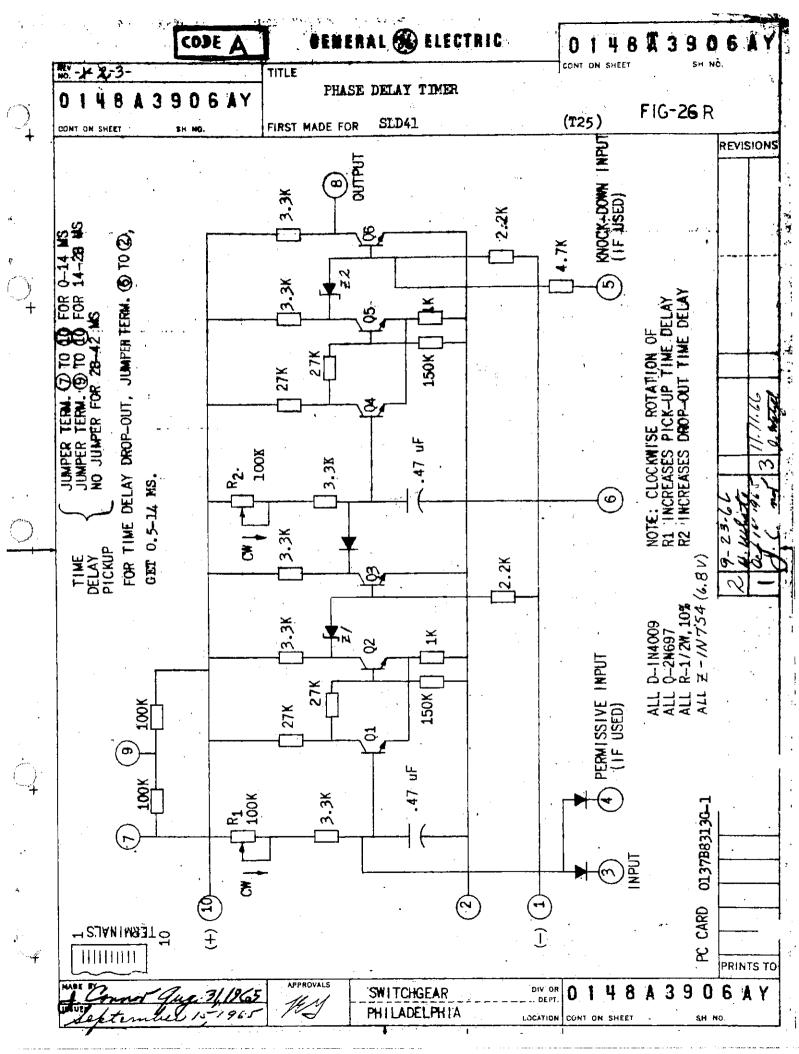

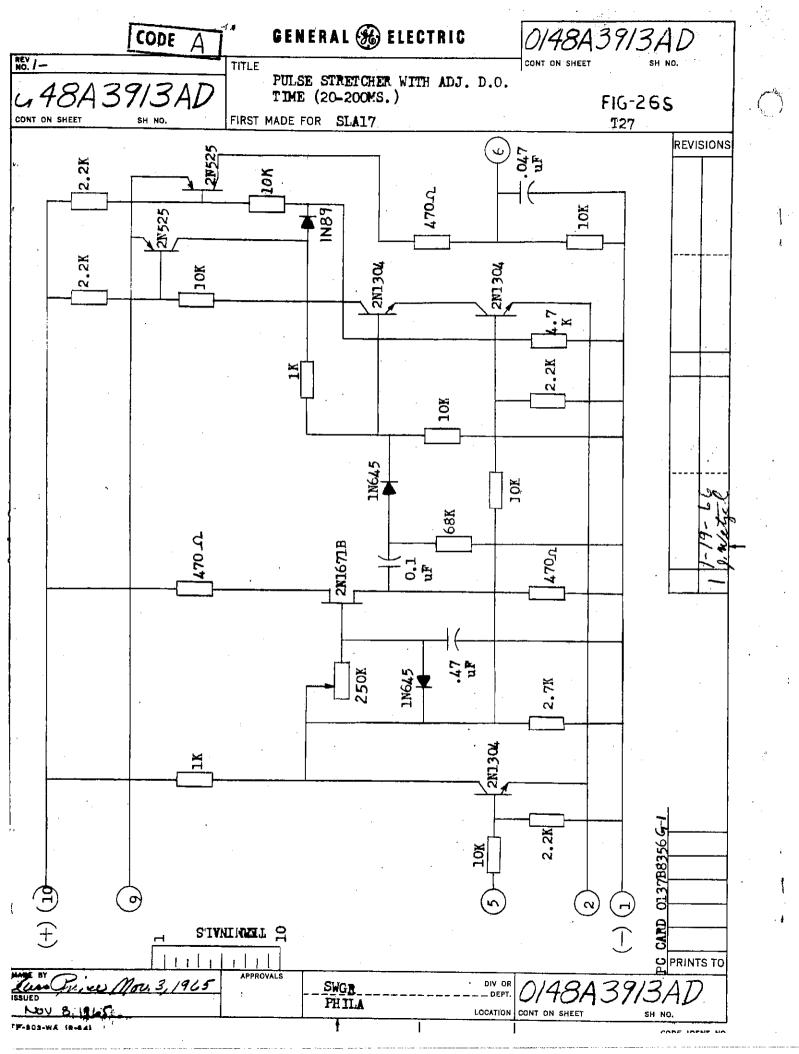

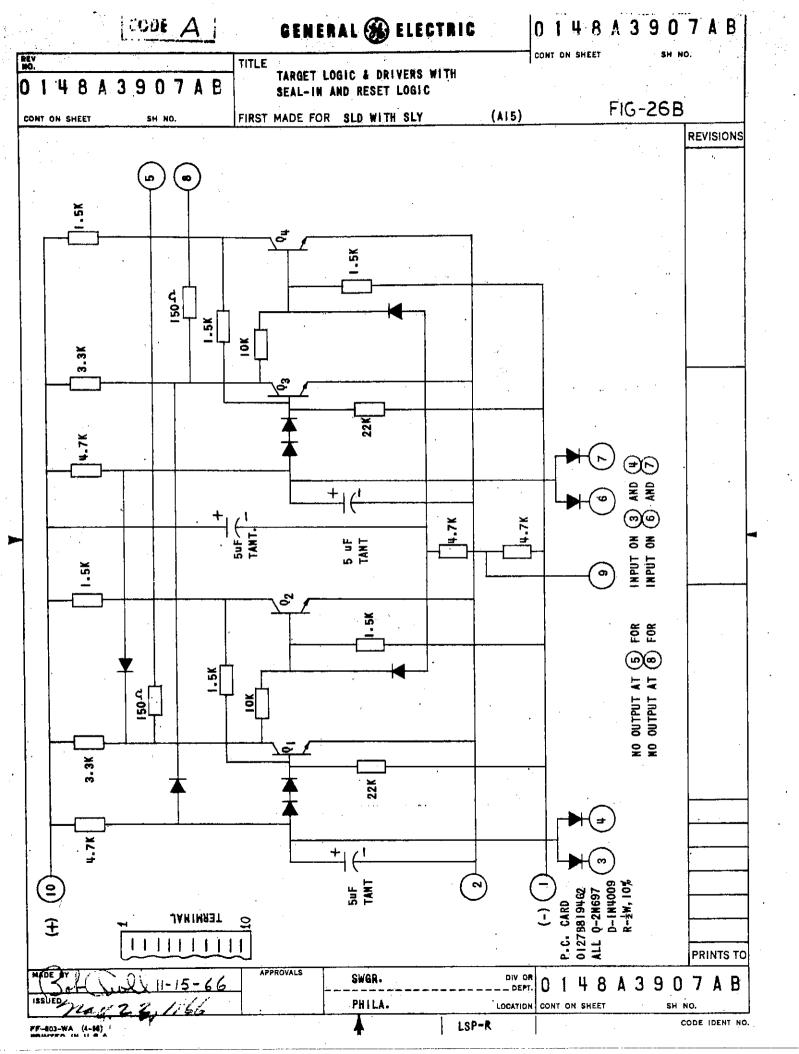

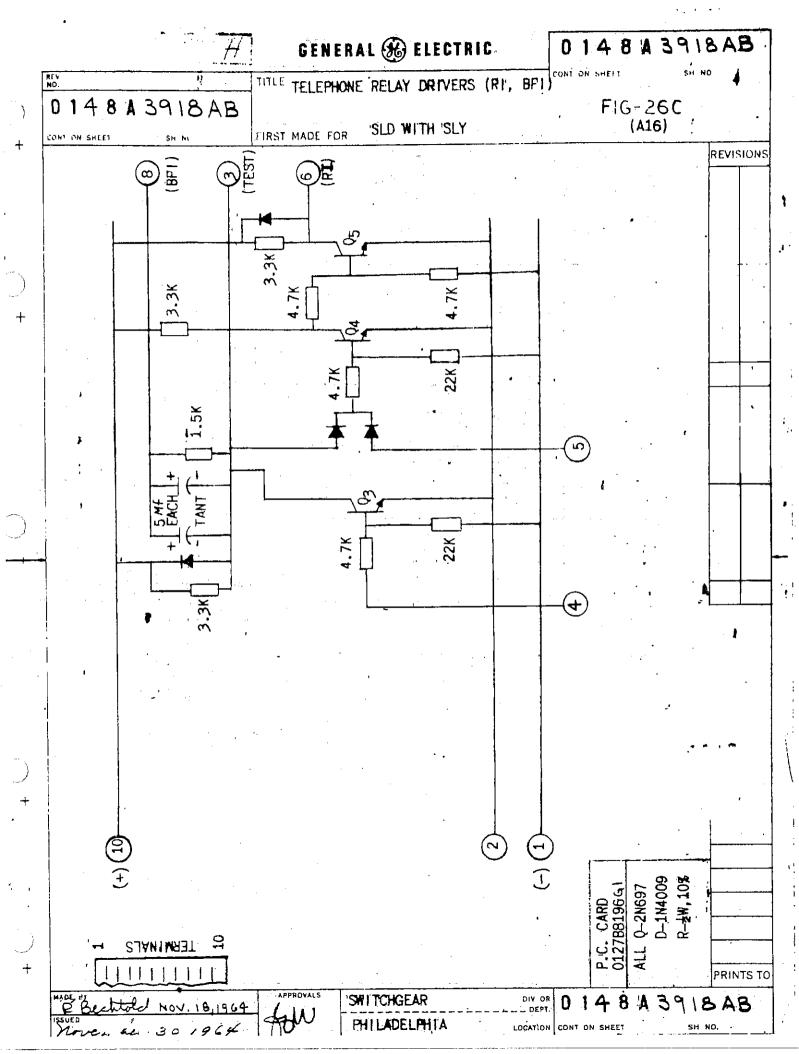

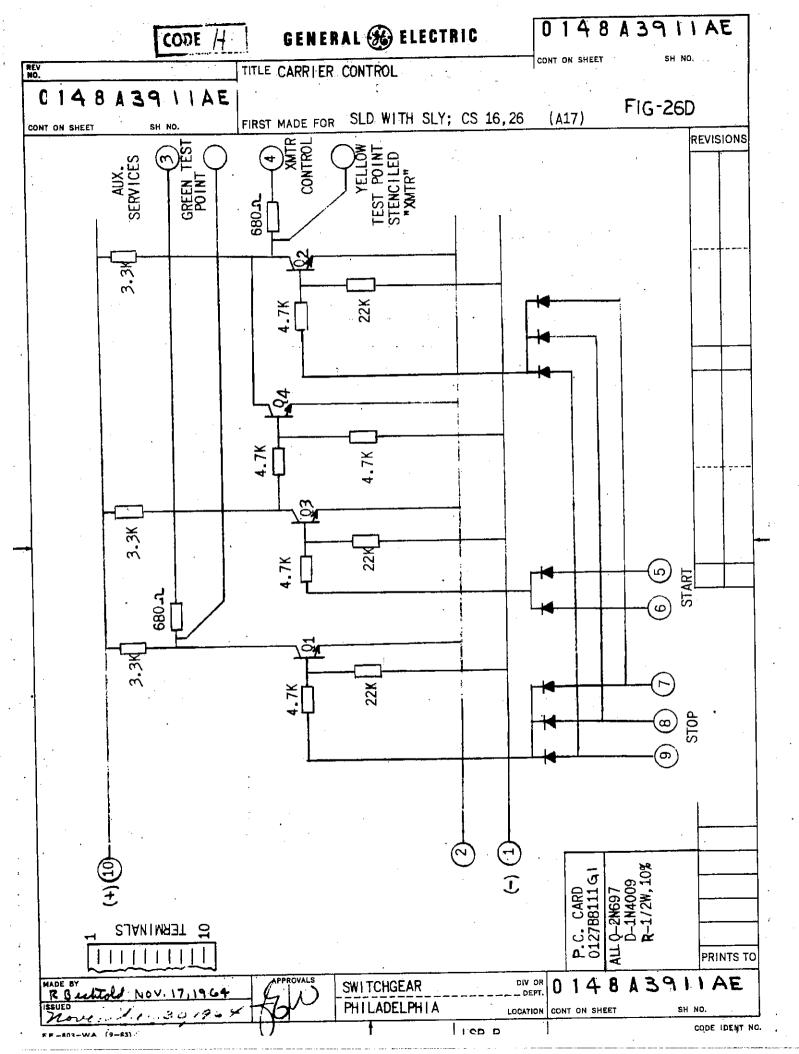

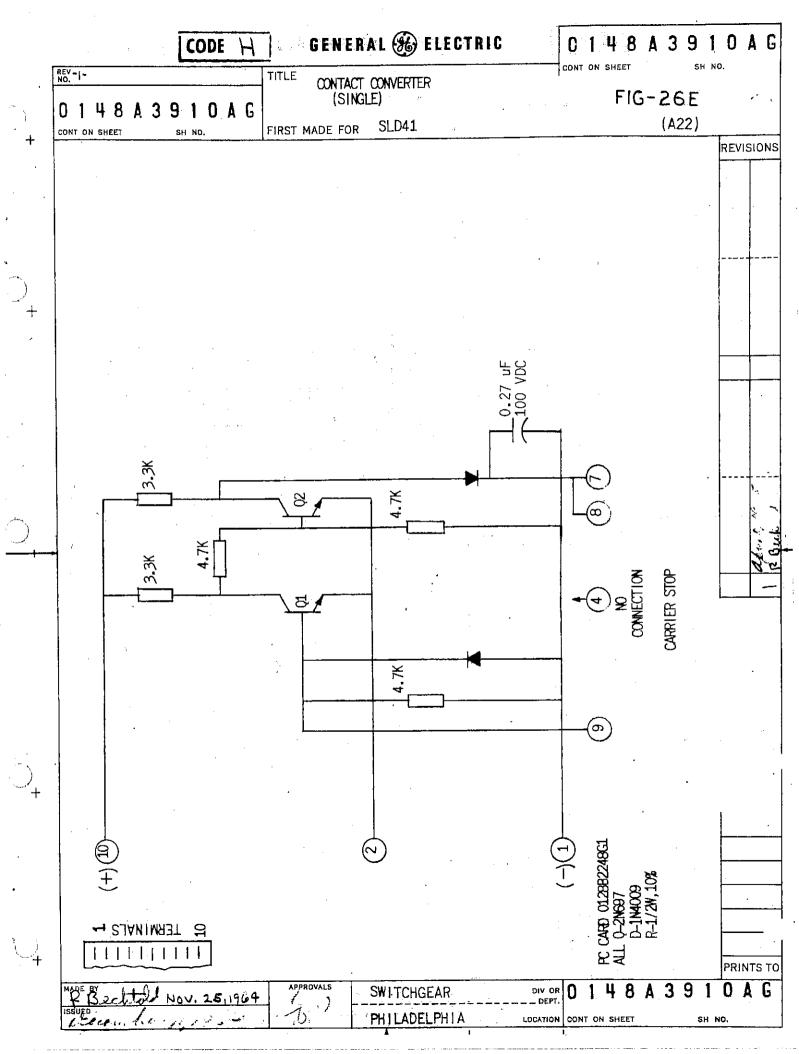

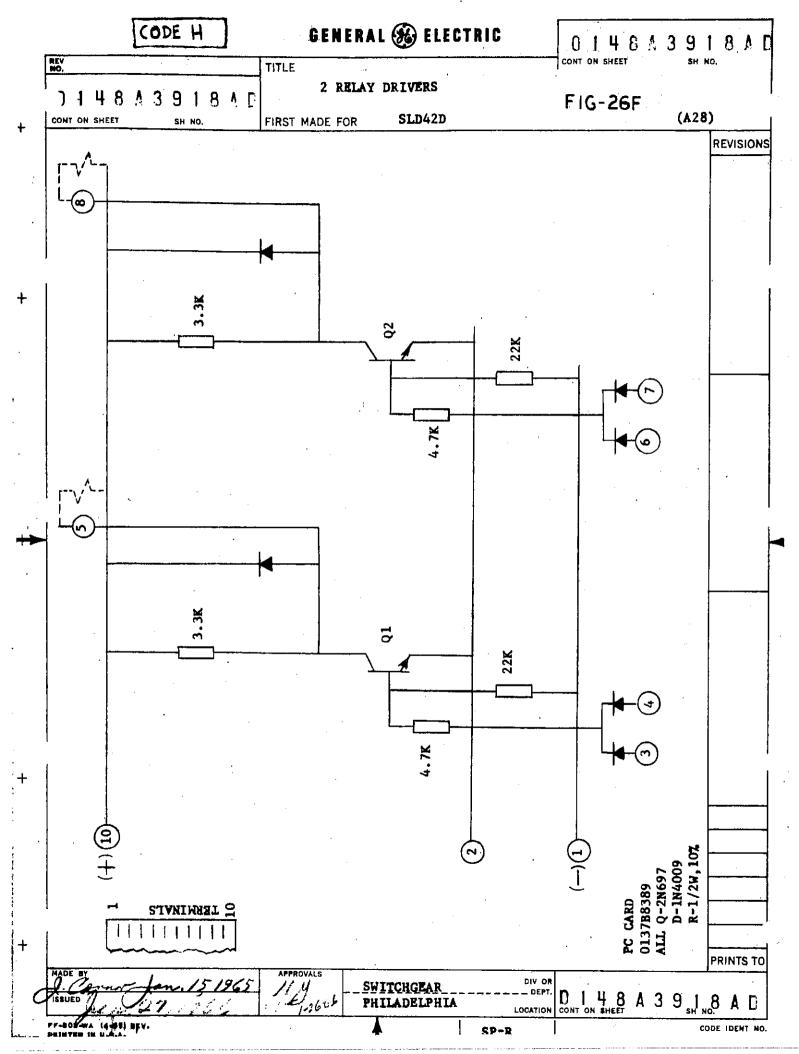

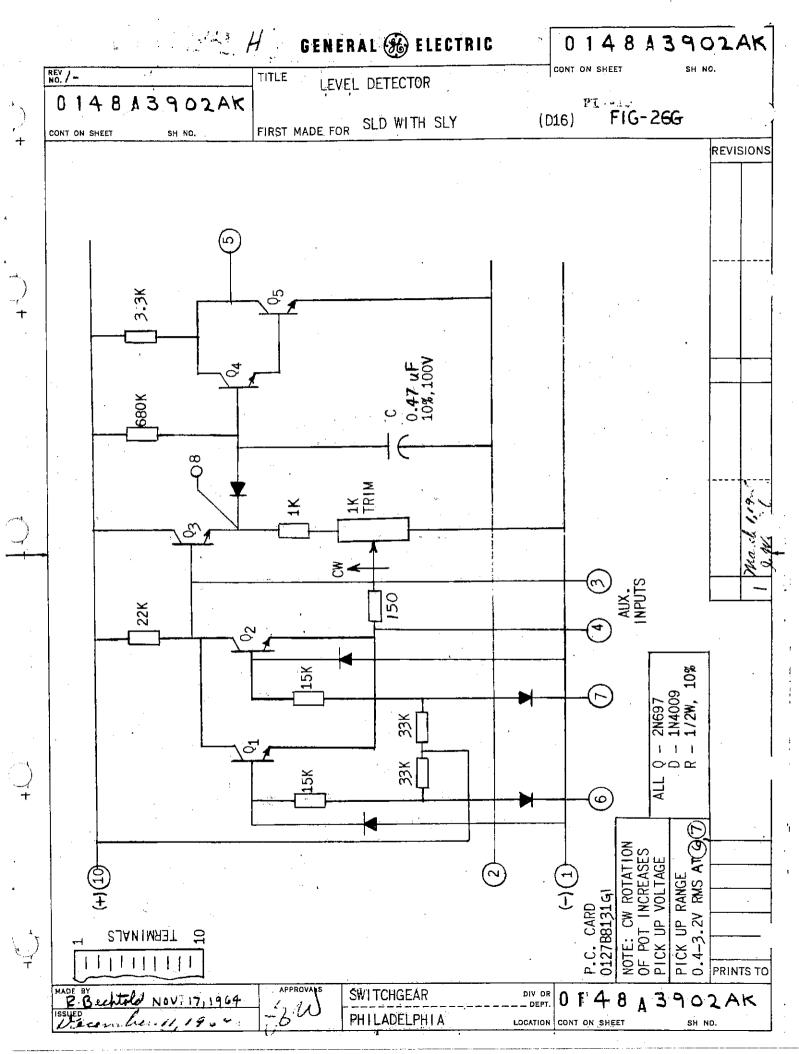

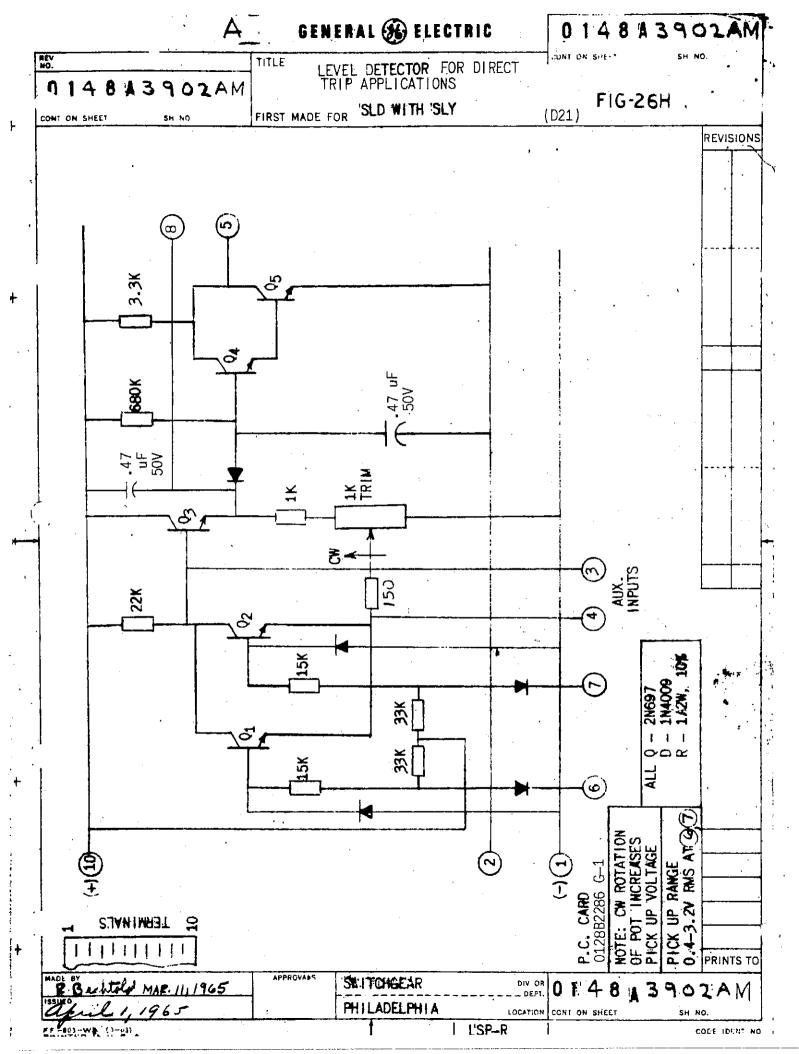

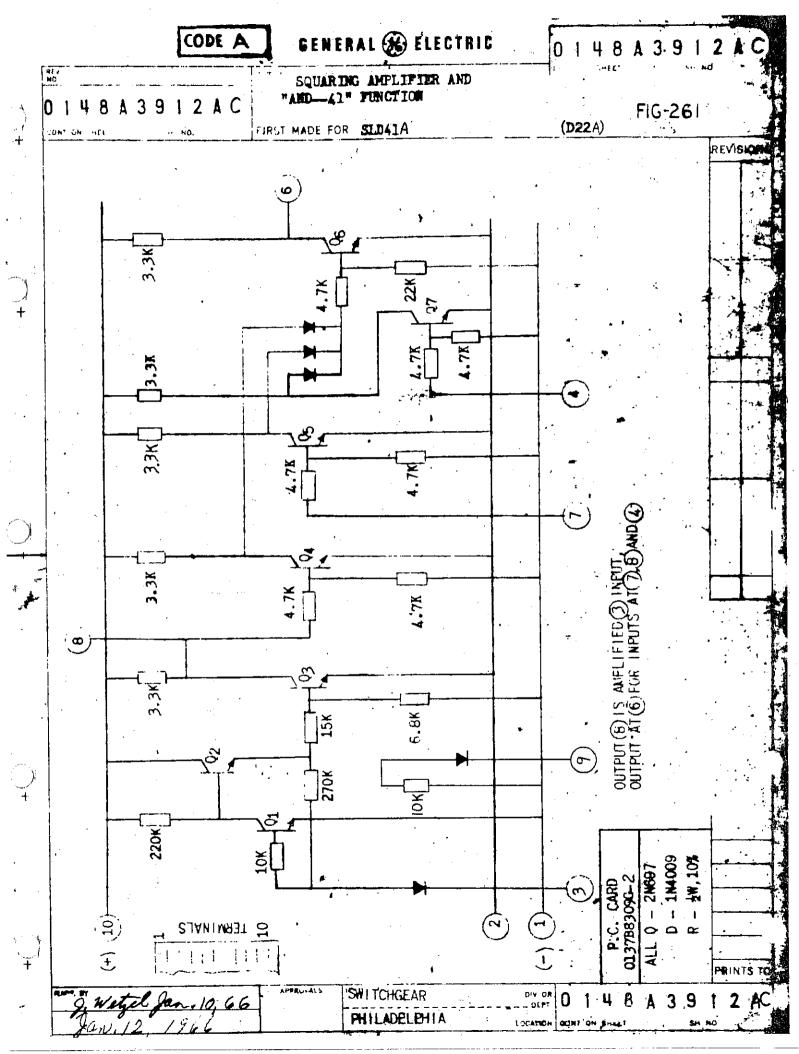

| BURDEN<br>ADJUSTMENT RANGES<br>OPERATING TIME                                                                                                                                                                                                                                                                                                                                                                               | 2<br>3<br>3                                                                                    | 23 LEVEL DETECTOR TEST CONN. 24 PHASE DELAY SETTING TEST CONN. 25 PHASE DELAY BY LOCAL SIGNAL 26A-26S - PRINTED CIRCUIT CARD DIAGS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OPERATING PRINCIPLES PHASE COMPARISON NEGATIVE SEQUENCE NETWORK POSITIVE SEQUENCE NETWORK LOGIC CIRCUITS OUTPUT CIRCUITS                                                                                                                                                                                                                                                                                                    | 3<br>3<br>4<br>5<br>6<br>8                                                                     | 20. 230 (MAN) 25 (2.1001) WIND PANOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| APPLICATION GENERAL INFORMATION REQUIRED CALCULATION OF SETTINGS SAMPLE CALCULATIONS                                                                                                                                                                                                                                                                                                                                        | 9<br>9<br>11<br>12<br>16                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TESTING GENERAL NETWORK BALANCE CHECK CT PHASING AND POLARITY LEVEL DETECTOR ADJUSTMENT TRANSMITTER DRIVE SYMMETRY PHASE DELAY ADJUSTMENT TRIP INTEGRATOR TIME CHECK RB LOGIC PULSE STRETCHER CHECKS G4 TRIP LEVEL ADJUSTMENT OUTPUT CHECKS                                                                                                                                                                                 | 18<br>18<br>21<br>22<br>23<br>24<br>27<br>28<br>28<br>29                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MAINTENANCE PERIODIC TESTS TROUBLE SHOOTING SPARE PARTS                                                                                                                                                                                                                                                                                                                                                                     | 29<br>29<br>30<br>30                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### ADDENDUM

### TYPE SLD42D1, AND SLD42D2 RELAY

This supplement in addition to the attached booklet comprises the instructions for the SLD421 and 2 relays, which were modified after field installation.

The modifications are discussed below:

- 1. Filters were added to the positive and negative sequence network outputs to prevent operation on line pickup.

- 2. A redesigned squaring amplifier card (D22A) with reduced sensitivity to eleiminate operation during network delay.

- 3. The FDH card (D16H) was modified and the pickup setting increased. This was necessary to avoid operation on charging currents and reduce the possibility of tripping on decaying line currents after external fault clearing.

- 4. The G4 (D23) was modified to avoid overreach.

- 5. Modified the transient blocking card (T20) and adjusted pickup time to 35 ms. The avoided blocking on delayed internal fault clearing.

The internal connections for the tap block and logic units are shown in figures 1 and 2 respectively. These supersede those internals illustrated in the attached booklet (fig. 11 and 14). The internals for the printed circuit cards referred above are shown in GEK-7364.

The application section for the modified SLD42D relay is below, and supersedes that application section in the attached book.

#### APPLICATION

#### GENERAL

The Type SLD42D phase comparison relays in conjunction with SLYL phase relays are particularly adapted to the protection of transmission lines, where the presence of mutual inductance with split busses or series capacitor compensation makes the application of directional comparison relaying difficult.

The SLD42 relay employs positive and negative sequence excitation. This is accomplished by passing selected phases of the CT secondary current through a positive and then a negative sequence filter. A portion of the single phase output of the positive sequence filter is then vectorially subtracted from the full single phase output of the negative filter to yield a single phase keying quantity that is proportional to:

$$I_k = I_2 - \frac{I_1}{K}$$

(1)

where K can be set for 5, 7, or 10. The phase angle of this quantity is compared with the phase angle of a similarly obtained quantity at the remote end of the line provided that the negative sequence fault detectors FDL, FDH, and the signal magnitude detector FDM operate for either an internal or external fault.

The basic concepts of mixed excitation is to have the negative sequence signal  $(I_2)$  dominate the positive sequence signal  $(I_1/K)$  for all faults, (except three phase faults), hence for all unbalanced faults the phase comparison will essentially be on a negative sequence basis. For three phase faults there will be no negative sequence current (except that which results from unbalances introduced by such things as non-transposition of lines, current transformer saturation, or load unbalance), thus phase comparison will be on a positive sequence basis.

These instructions do not purport to cover all details or variations in equipment nor to provide for every possible contingency to be met in connection with installation, operation or maintenance. Should further information be desired or should particular problems arise which are not covered sufficiently for the purchaser's purposes, the matter should be referred to the General Electric Company.

For various faults and fault locations the relative magnitudes of  $I_1$  and  $I_2$  must be known to calculate the quantity  $I_k$ . It is important to recognize that neglecting load current  $I_1$  and  $I_2$  in equation (1) will be equal for phase and ground fualts. For double phase to ground faults  $I_1$  will always be greater than  $I_2$  by an amount that depends on the ratio of the system zero sequence to positive sequence impedance. As a result, it is necessary to consider double phase to ground faults as well as single phase to ground faults in the application of the SLD42 relays. Given a fault location, the negative sequence component of current for a phase to phase fault will always be half of the three phase positive sequence fault current, and equal to or greater than the negative sequence component in a double phase to ground fault. Consequently, there is no need to consider phase to phase faults separately.

If the SLD42 relay is applied to long, heavily loaded HV or EHV transmission lines with series capacitor compensation, the influence of load current, shunt capacitance, and series capacitors requires more detailed consideration for optimum reliability than would be necessary for short lines.

#### LOAD CURRENT

For an internal fault with no load flow the keying signals at the two ends are in phase, and as shown in Fig. 10, the received carrier is in phase with the transmitted carrier. The presence of a substantial load current, which continues to flow through the line during an internal fault, may cause the keying signals at the two ends to be shifted out of phase. Because of the 3 millisecond pickup setting of the integrator timer, tripping is obtained when the phase angle between the keying signals at the two ends of the line is  $115^{\circ}$  or less. Actually the phase angle criterion for determining settings is to restrict the keying signal angular difference to  $60^{\circ}$  or less. This provides a margin of  $55^{\circ}$  to allow for additional phase shift due to factors other than load flow.

${\rm I}_1$  of equation (1) is the superposed sum of the prefault load component and the fault component as determined by Thevenin's theorem. The influence of load current on equation (1) is most readily obtained by evaluating the keying signal,  ${\rm I}_{kF}$ , resulting from fault components of current and comparing it with the keying signal resulting from the load component of  ${\rm I}_1$ ,  ${\rm I}_{kL}$ . Equation (1) may be rewritten:

$$I_{k} = I_{2} - (\frac{I_{1F} + I_{1L}}{K})$$

$$I_{k} = (I_{2} - \frac{I_{1F}}{K}) - \frac{I_{1L}}{K}$$

$$I_{k} = I_{kF} - I_{kL}$$

(2)

Assuming that the positive source impedance is equal to the negative source impedance and the sources at both ends of the line have the same impedance angle, then  $I_{kF}$  will have the same phase angle at both terminals but opposite in polarity. It is assumed that  $I_{kL}$  may have any phase relationship to  $I_{kF}$ ; the worst angle is a function of the negative (/positive/) distribution factor, C, as illustrated in Fig. 15.

The optimal value of K is the smallest value that will restrict the phase angle between keying signals on unbalanced faults to  $60^{\rm o}$ , thereby providing maximum sensitivity on 3 phase faults. The method for selecting the optimal value of K is covered under CALCULATION OF SETTINGS.

#### SHUNT CAPACITANCE

The current slowing into the negative sequence shunt capacitance during an external fault will cause the negative sequence currents realized by the two terminals to be of different magnitude. The negative sequence fault detectors FDH and FDL have a difference in setting larger than the negative sequence current flowing in the shunt capacitance. This is to assure that the tripping element FDG is not picked up at one end before the carrier start element FDL is energized at the other.

With the fault keying signal  $I_{kF}$  at one terminal larger than it is at the other for an external fault, and with the magnitude of  $I_{kL}$  equal to the mean of the two  $I_{kF}$  magnitudes, it is possible to produce in phase keying signals,  $I_k$ , at the two terminals (provided  $I_{kF}$  and  $I_{kL}$  are in phase at each end). This could produce an undesired trip for an external fault since in phase keying signals produce a trip output. To overcome this possibility the FDM function, which is operated by  $I_k$ , should be set above the maximum value of  $I_k$  expected for the above condition to prevent phase comparison from occurring.

The inrush into the shunt capacitance on line energization (particularly with unequal pole closing of the breaker) may limit the setting of FDH which can be safely used.

#### SERIES CAPACITANCE

The series capacitance may affect the phase comparison indirectly if spurious carrier is generated when the protective gaps flashover. It is anticiapted that these bursts of spurious carrier will be in the range of one millisecond, which could reset the phase comparator timer if allowed to block AND45.

### INFORMATION REQUIRED FOR SETTING CALCULATIONS

In order to establish the optimum settings for the SLD42 relay it is necessary to obtain the following system data:

- 1. Maximum load current present in the line for each system configuration to be considered.

- 2. Mimimum positive sequence fault current present in each terminal for internal three phase faults near each terminal and the midpoint of the line for each system configuration.

- 3. Mimimum positive and negative fault current present in each terminal for single line to ground faults near the midpoint of the line and near each terminal for each system configuration.

- 4. Mimimum positive and negative sequence fault current present in each terminal for double line to ground faults near each of the terminals for each system configuration.

- 5. The ratio  $R_0$  (ØG) of  $I_0$  for single line to ground faults to  $I_{30}$  for 3 phase faults at each fault location and each system configuration.

If the information is not available directly in the form required, it can be derived if the fault study provides for each location:

- 1. The total 3 phase fault current and the distribution factors.

- 2. The total zero sequence fault current for a single line to ground fault.

- 3. The maximum load current.

The total negative sequence fault current for a single line to ground fault will equal to  $I_0$ , as will the total fault component of the positive sequence current,  $I_{1F}(DG)$ .

The ratio  $R_0(\Omega G)$  may be used to obtain the positive and negative sequence components of fault current for double line to ground faults in conjunction with I30 at the same fault location.

$$I_{1F}(\emptyset \emptyset G) = R_1(\emptyset \emptyset G) \times I_{3\emptyset} = I_{3\emptyset} \times \frac{1 - R_0(\emptyset G)}{2 - 3R_0(\emptyset G)}$$

$R_1$  (00G) can be read directly from Figure 16A.

$$I_2(\emptyset\emptysetG) = R_2(\emptyset\emptysetG) \times I_3\emptyset = I_3\emptyset \times \frac{1 - 2R_0(\emptysetG)}{2 - 3R_0(\emptysetG)}$$

$R_2(\emptyset\emptyset G)$  can be read directly from Figure 16B.

The distribution of negative and positive sequence components of fault current at terminals X and Y can be obtained by multiplying the total sequence components of fault current by the distribution factors  $\mathsf{C}_\mathsf{X}$  and  $\mathsf{C}_\mathsf{Y}$ .

### CALCULATION OF SETTINGS

The installation adjustments of the SLD42 consist of pickup settings of G4, FDH, FDL, FDM and the value of K which determines the relative emphasis on the positive and negative sequence inputs to the keying signals. A sample calculation is made for the system in Figure 17A which is presumed to provide for the protected line the most onerous application from a consideration of load studies and equipment outages. Figure 17B illustrates the tabulation of data for the sample system.

Before calculating  $I_2(\emptyset G)_X$  (which is equal to  $I_2(\emptyset G)x$   $C_X$ ,  $R_0(\emptyset G)$  should be evaluated to ascertain if the lowest negative sequence current is associated with single line to ground faults or double line to ground faults. If  $R_0(\emptyset G)$  is 0.333 or lower,  $I_2(\emptyset G)$  will be equal to or lower than  $I_2(\emptyset G G)$ , and  $I_2(\emptyset G)$  should be calculated. Conversely, if  $R_0(\emptyset G)$  is larger than .333,  $I_2(\emptyset G G)$  will be smaller, and should be calculated.

#### PICKUP SETTINGS OF FDH AND FDL

The FDL level detector should be set as low as possible without risk of its operating on the maximum expected load unbalance, unless the possibility of continuous keying of the channel is not objectionable. For many applications the minimum FDL pickup of 0.2 amperes negative sequence will be applicable.

The FDH level detector must be set such that it will respond to any internal unbalanced fault with a margin of at least 50 percent. That is, the minimum negative sequence current for an unbalanced fault at any location on the protected line must be at least 1.5 times the negative sequence pickup of FDH. An additional requirement on FDG pickup setting is that it be sufficiently above FDL to insure security on external faults. The setting of FDH must establish a margin between the local blocking level (FDL pickup) and the tripping level at the remote terminal (FDH pickup). For two terminal line applications the recommended margin is expressed by the following equation:

$$FDH = (\frac{4}{3}) FDL$$

If there is significant negative sequence charging current flowing into the protected line during an external fault, it will tend to negate some of the margin provided by the above equation.

Therefore, to account for charging current the equation for FDH pickup becomes:

$$FDH = (\frac{4}{3}) FDL + I_{C2}$$

where I<sub>C2</sub> = negative sequence charging current

flowing in the protected line section during an external fault.

The negative sequence charging current in the equation above should be:

$$I_{C2} = 0.5 \times I_{C1}$$

(3)

where I<sub>C1</sub> = positive sequence charging current

$$I_{C1} = \frac{V_{LN}}{Z_{SC}}$$

where  $Z_{SC}$  = total impedance of the distributed shunt capacitance

If shunt reactors are present the steady state value of charging current will be diminished. However, this effect should not be considered since coordination is necessary on a transient basis. The value of Ic2 in equation (3) is an empirically derived value that has been generally applicable where breakers with pre-insertion resistors are used.

A possible restriction on FDL is that it should be set above the negative sequence current that may result from maximum load current flowing through an untransposed line, otherwise continuous carrier may be transmitted.

#### SELECTION OF K FACTOR

As noted under general comments, the minimum value of K should be selected. For less onerous applications, K = 5 should be selected. K = 5 may be used with an ample margin of safety if the minimum load current is less than 125% of the smallest  $I_2(\emptyset G)_y$ ,  $I_2(\emptyset \emptyset G)_x$  and  $I_2(\emptyset \emptyset G)_y$ . If this relationship is not true, a more rigorous evaluation of the optimum value of K is necessary and the tabulation in Figure 17B should be completed.

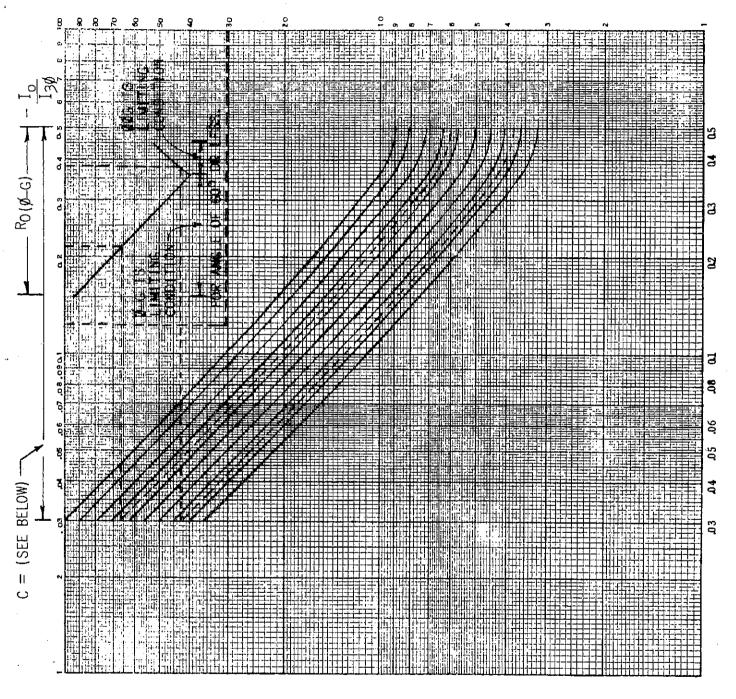

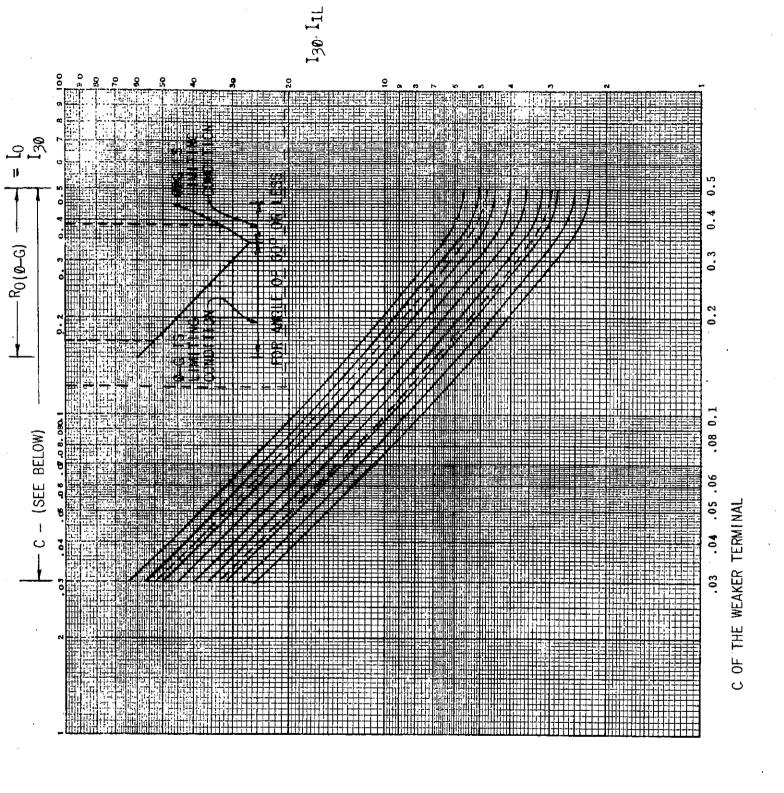

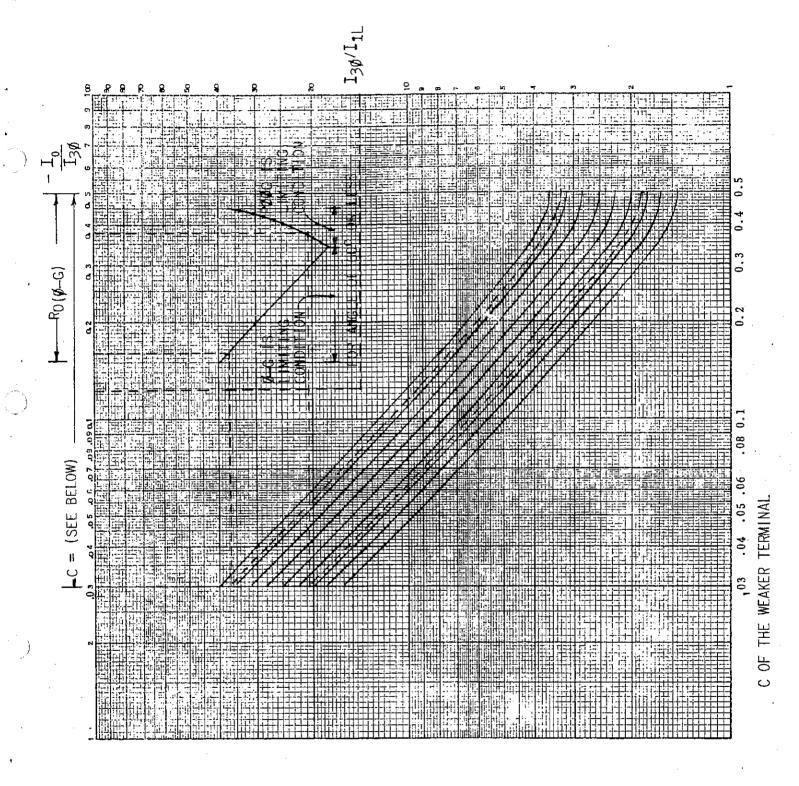

The : in Figures 18A, B and C are provided to allow the selection of the K factor directly, utilizing the data tabulated in Figure 17B. The curves are based on the following:

- The angle between the keying signals at the two terminals should be no more than 60°.

- 2. A safety margin is obtained by using only 75% of the calculated negative sequence current.

With reference to Figure 18A, each fault location is checked by plotting the ratio of three phase fault current to load current,  $I_{30}/I_{1L}$ , and the lower of  $C_X$  and  $C_Y$ . If the point is at the upper right of

the top one of the parallel curves, K = 5 will be suitable for that fault location.

If the point falls between the top and the bottom curve, enter the graph at the proper point on the  $R_0(\slash\hspace{-0.05cm}G)$  scale at the top of the graph, proceed down until the V curve is reached, then horizontally to the left, until the distribution factor C = .03 is intersected. Draw a curve parallel to the existing curve which passes through the intersection of the horizontal line drawn and C = .03. This construction is shown in dashed lines for two arbitrary values of  $R_0(\slash\hspace{-0.05cm}G)$ ; one where  $\slash\hspace{-0.05cm}G$  is limiting. If the point  $C_X$  (or  $C_Y$ ) and  $C_Y$  and  $C_Y$  are subsequently plots above and to the right of the curve constructed for the specific value of  $C_Y$  (or  $C_Y$ ) and  $C_Y$  will be satisfactory. If this point plots below this curve then the procedure must be repeated, starting with K = 7, Figure 18B.

If the initial plot of C and  $I_{30}/I_{1L}$  lies below and to the left of the bottom curve then K = 5 is not suitable, and the procedure must be repeated, starting with K = 7, Figure 18B. If the procedure is repeated for K = 7 and K = 7 is found unsuitable then proceed to K = 10, Figure 18C.

When the value of K has been found for all fault conditions that may provide the limiting case, select the largest value of K (5, 7, or 10) and apply at both terminals. Different values of K at the terminals could result in a phase shift between the keying signals at each terminal for an unbalanced external fault, with false tripping as a possible consequence.

If desired the angular displacement between the keying signals may be obtained by plotting a phasor diagram of the two keying currents produced by the selected value of K. Figure 19A illustrates the phasor diagram for the fault at F3 where the  $\emptyset G$  fault is the limiting condition. IKF is obtained at terminal x by plotting .75I<sub>2</sub>( $\emptyset G$ )x to an appropriate scale and vectorially subtracting the positive sequence fault component at X, IIF( $\emptyset G$ )X/K. Since the worst case of a phase A to ground fault is assumed IIF( $\emptyset G$ )X = I2F( $\emptyset G$ )X, and IIF( $\emptyset G$ )X/K is subtracted directly from .75I<sub>2</sub>( $\emptyset G$ )x From Figure 15, the worst angle between IKL and IKF can be obtained for the lower value of C (Cx). At this angle, IKL is drawn to the same scale as I2( $\emptyset G$ )X and the angle ( $\emptyset 1$ ) between IK and IKF is obtained by measurement. Similarly at terminal Y, 0.75 I2( $\emptyset G$ )Y can be plotted and IIF( $\emptyset G$ )Y/K can be subtracted directly from it to obtain IKF. IKL can be added to IKF (IKL at Y is 180° out of phase with IKL at X) to obtain IK at terminal Y. The angle between IKF and IK at Y ( $\emptyset 2$ ) is added to  $\emptyset 1$  to obtain the total angular displacement between the keying signals at the two terminals.

The angular displacement between the keying signals at the two terminals can be plotted in a similar manner for a case where  $\emptyset\emptyset$ G fault is the limiting type of fault, with two exceptions. I1F( $\emptyset\emptyset$ G) $\chi$  is not equal to I2( $\emptyset\emptyset$ G) and must be obtained from the tabulation in Figure 17B. I1F( $\emptyset\emptyset$ G) $\chi$  will not subtract directly from I2( $\emptyset\emptyset$ G) $\chi$  in the worst type of fault, but at 60°. The fault at location F1 is plotted in Figure 20A.

If the line under consideration is series capacitor compensated, K = 7 should be used, and there is no need to follow the procedure above. This K value was determined on an empirical basis and represents an optimum compromise value.

### SETTING OF FDM

As explained previously a combination of load current and shunt capacitance can combine to produce a false trip on an external fault. To assure that keying cannot occur for this case, FDM should be set above 50% of the keying signal produced by the positive and negative sequence charging currents.

$$FDM = I_{c2} + \frac{I_{c1}}{K}$$

In this case:  $I_{c1} = 0.5 \frac{V_{LN}}{Z_{shunt}}$

$$where: Z_{shunt} = \frac{Z_{sc}}{Z_{sc} + Z_{sr}}$$

$$Z_{sc} = total \ impedance \ of \ the \ distributed \ shunt \ capacitance$$

$$Z_{sr} = total \ impedance \ of \ the \ shunt \ reactors \ (if \ present)$$

$$I_{c2} = 0.25 \frac{V_{LN}}{Z_{shunt}}$$

$$FDM = \frac{0.25 \ V_{LN}}{Z_{shunt}} + \frac{0.5 \ V_{LN}}{(K)Z_{shunt}}$$

The above equation includes a safety margin of 2.

The minimum value of keying signal for an internal fault can be obtained by taking the minimum value of the fault component of the keying signal, IKF, and subtracting the load component of the keying signal, IKL, directly from it.

$$I_K$$

(MIN.) =  $|I_{KF}$  (MIN)| -  $|I_{KL}$  (MAX)|

$I_K(MIN)$  should be compared with the setting for FDM to assess the margin of safety. Figures 19B and 20B illustrate the minimum keying signal for fault locations F1 and F3.

#### PICKUP SETTING OF G4

This unit is non-directional and therefore must be set above the maximum through ground fault current ( $3I_0$ ) for faults in either direction. A pickup setting equal to 125% of the maximum steady state through fault current is recommended. For the sample calculation, the maximum through fault current is assumed for faults at F1 and F3. However, if series capacitor compensated parallel lines exist, the maximum through fault current may occur for a fault on a parallel line after it opens at one terminal. On series capacitor compensated lines, a pickup setting equal to 200% of the maximum steady state through fault current is recommended.

Consideration must also be given to the possibility of unequal ploe closing of the circuit breaker when the line is reclosed at the second terminal. The G4 element must be set above the maximum load transfer over a single phase for the system conditions obtaining at the time of reclosure. The same margins should be obtained in this instance as mentioned previously.

### SAMPLE CALCULATIONS (refer to Figure 17)

Setting of FDH and FDL:

Set FDH =

$$2/3$$

( $I_2$  minimum) =  $(2/3)$  0.19 = 0.127 pu

This is the maximum value at which FDH may be safely set.

The maximum FDL setting may be determined from:

FDH =

$$\frac{4}{3}$$

FDL + I<sub>C2</sub>

FDL =  $\frac{4}{3}$  (FDH - I<sub>C2</sub>) = 0.75 (.127 -  $\frac{0.5}{6}$ )

FDL = .0327 p.u.

#### SELECTION OF K FACTOR:

Utilizing the procedure previously outlined it is found that K = 10 is required for faults at F2 and F3. K = 10 must therefore be used at both terminals.

#### SETTING OF FDM

$$FDM = \frac{0.25 \text{ V}_{LN}}{Z_{shunt}} + \frac{0.5 \text{ V}_{LN}}{(K)Z_{shunt}}$$

$$Z_{shunt} = \frac{(-j6) (j8)}{-j6 + j8} = j24$$

$$FDM = \frac{0.25}{24} + \frac{0.5}{(10) (24)}$$

$$= .0104 + .00208$$

$$= .0125 \text{ p.u.}$$

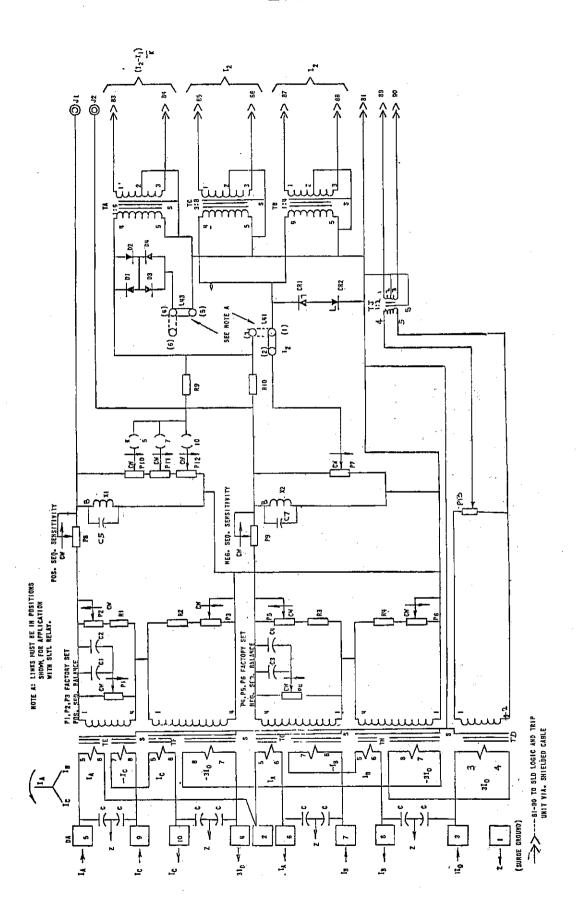

FIG. I (0165B2514-0) Internal Connections Diagram For The SLD42D Network Unit

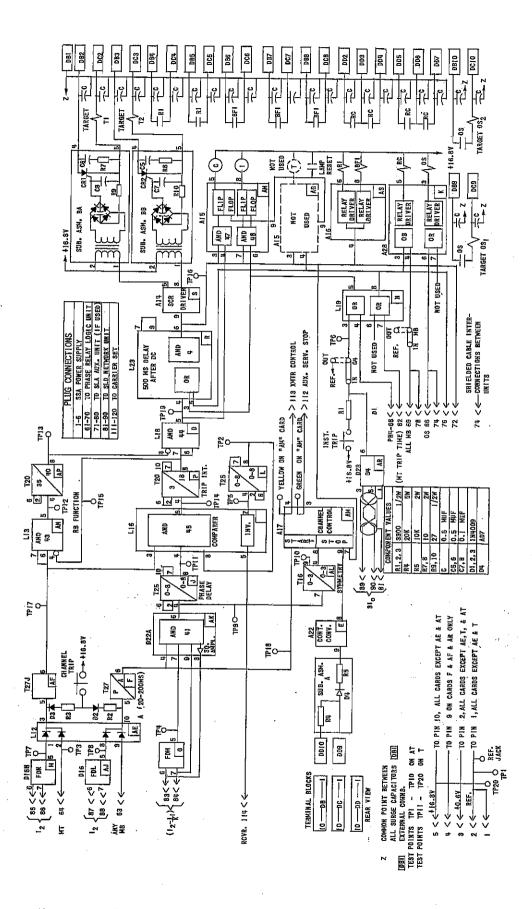

FIG. II ()165B2515-0) Internal Connections Diagram For The SLD42D Logic And Trip Unit

#### GEK-6877

### TYPE SLD42D RELAY

#### DESCRIPTION

### FUNCTIONS

The Type SLD42D relay is a solid state phase comparison pilot relay for differential protection of transmission lines on three-phase, phase-to phase, and phase-to-ground faults. The relay contains both positive and negative sequence networks and the associated phase comparison logic; FDL and FDH negative sequence fault detectors; FDM (positive and negative sequence) keying level detector; G4 direct-trip residual overcurrent function; two SCR (silicon controlled rectifier) trip circuits with hand reset series targets; and auxiliary relay contact outputs for RI (reclosing initiation), BFI (breaker failure initiation), OS (out-of-step), and RC (reclose cancellation).

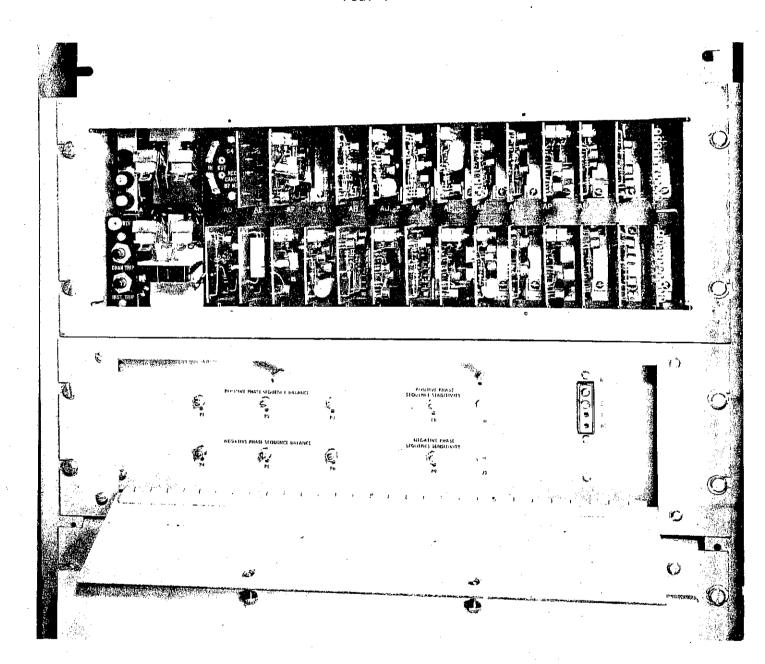

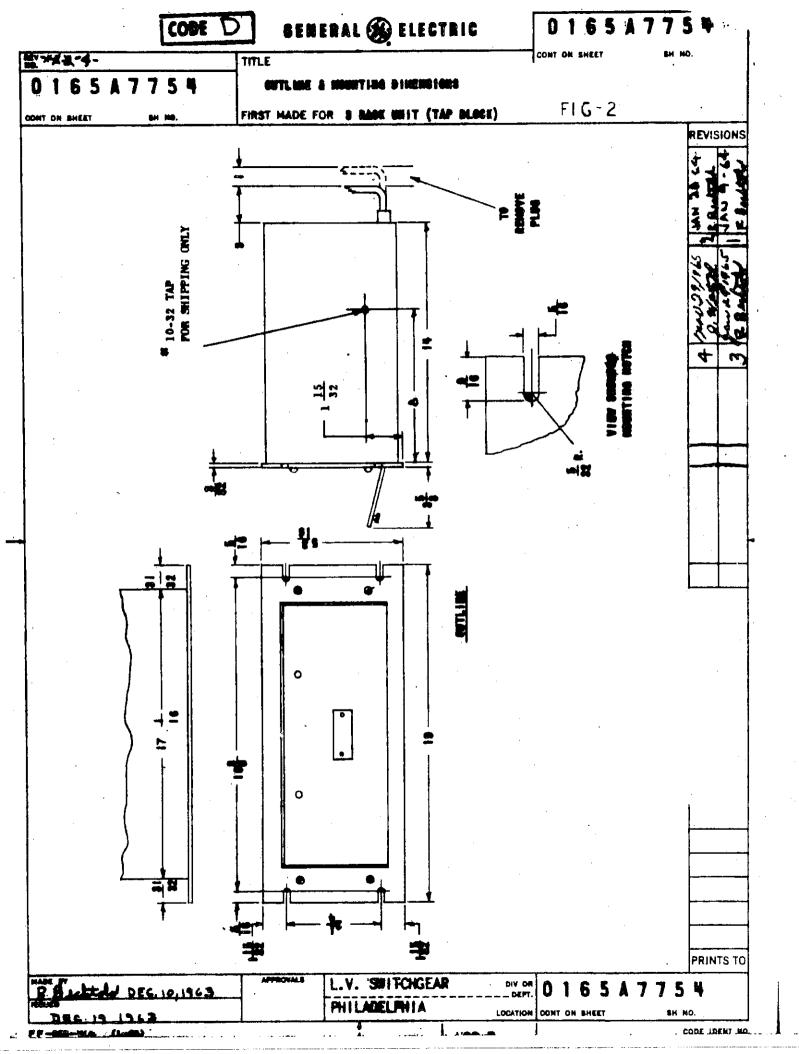

### NETWORK UNIT

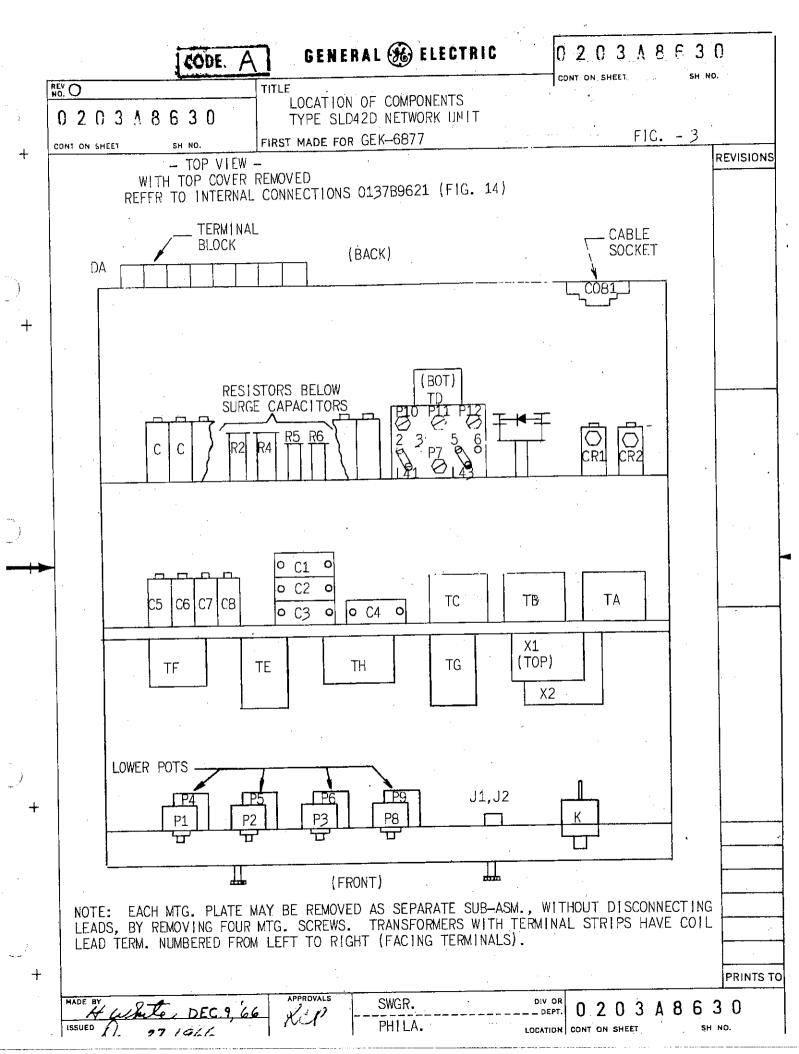

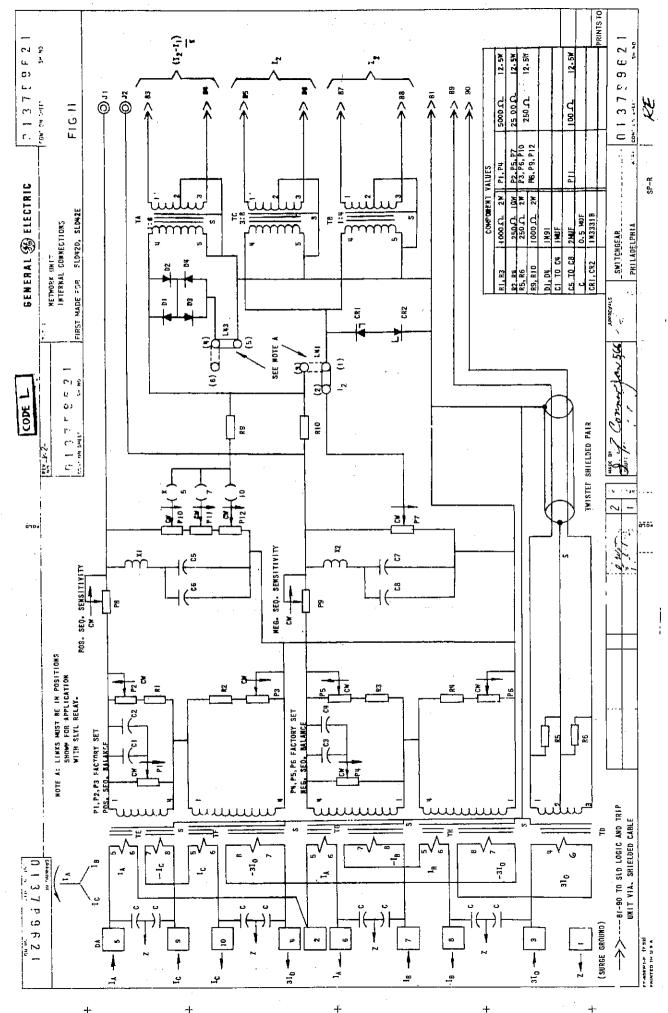

The SLD42D is packaged in two separate metal units suitable for mounting on standard 19-inch racks. The Network Unit, which is three rack-units high, includes the positive and negative sequence networks and associated adjustment potentiometers and tap block. The Network Unit also includes voltage limiter circuits and isolation transformers to couple the output voltage signals to the Logic Unit. Fig. 2 shows the outline and mounting dimensions for the Network Unit. The location of the various internal components of the Network Unit are shown in Fig. 3.

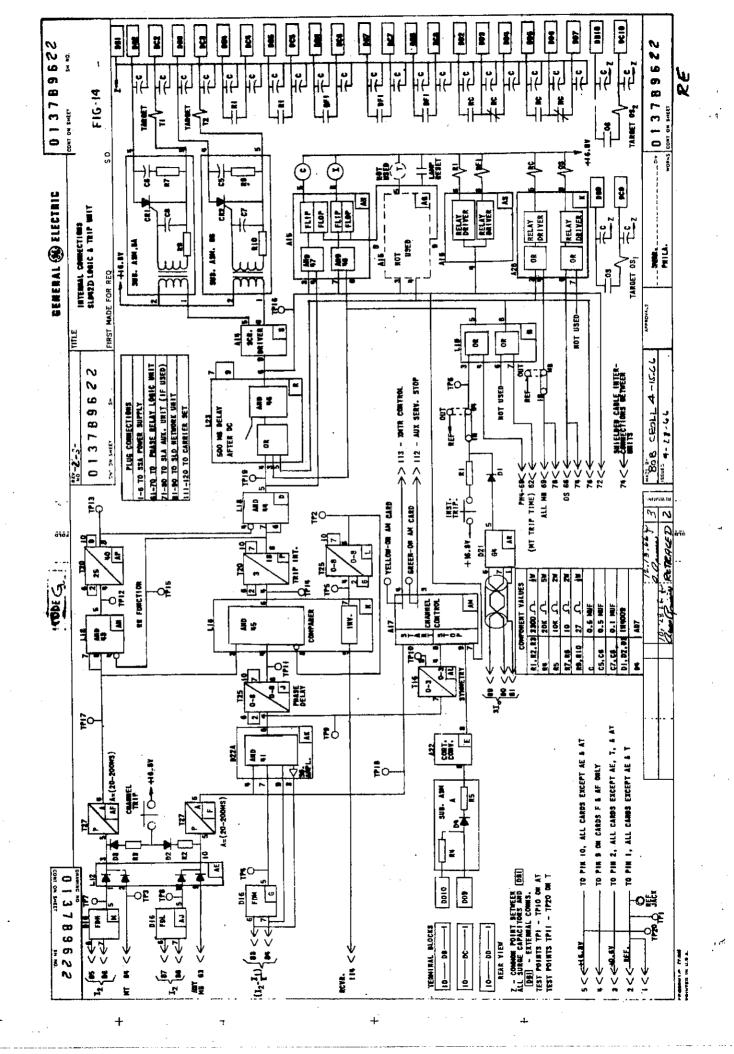

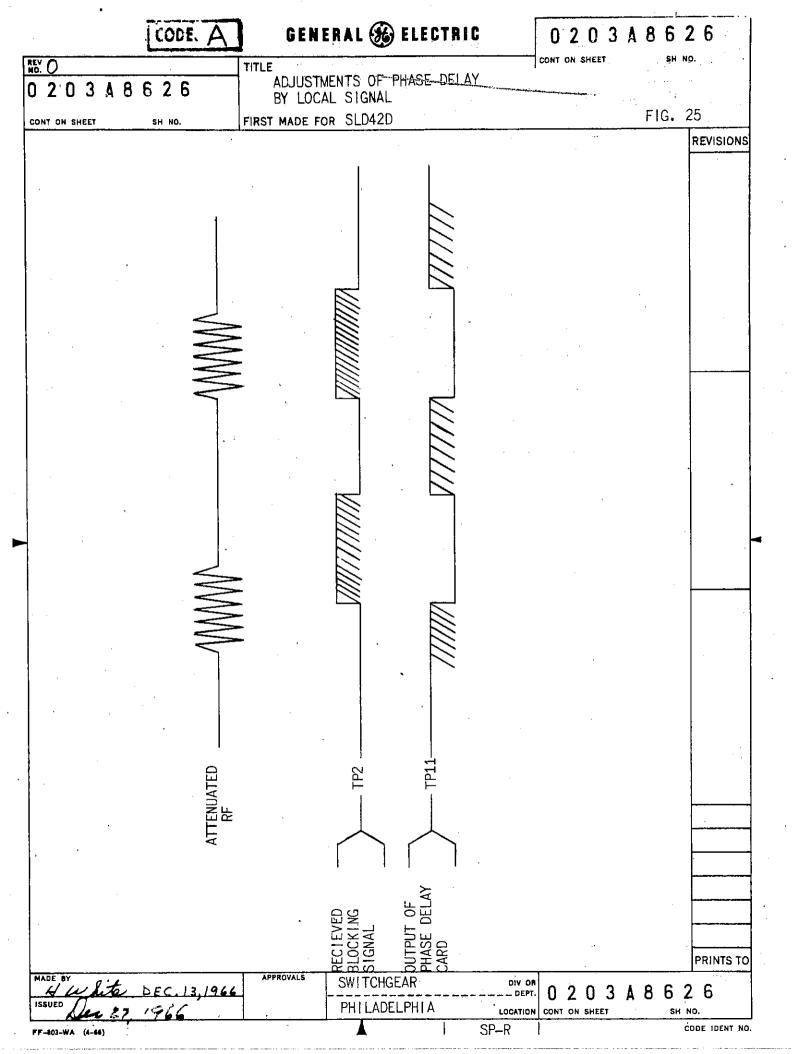

### LOGIC UNIT

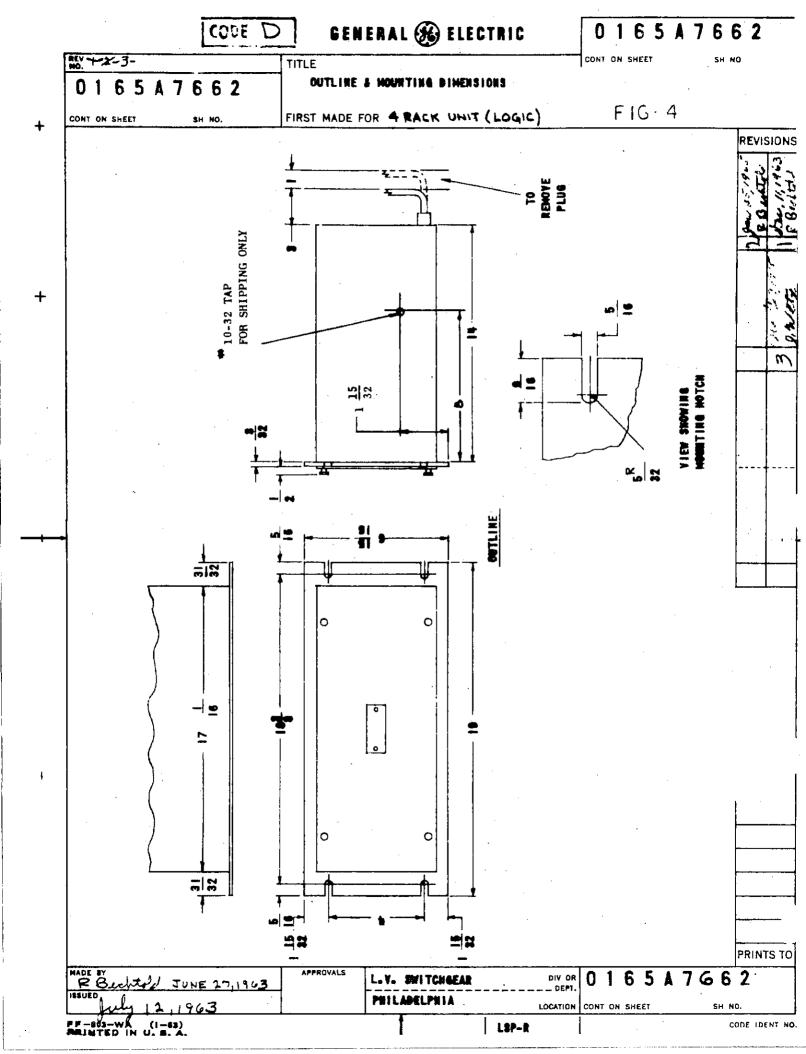

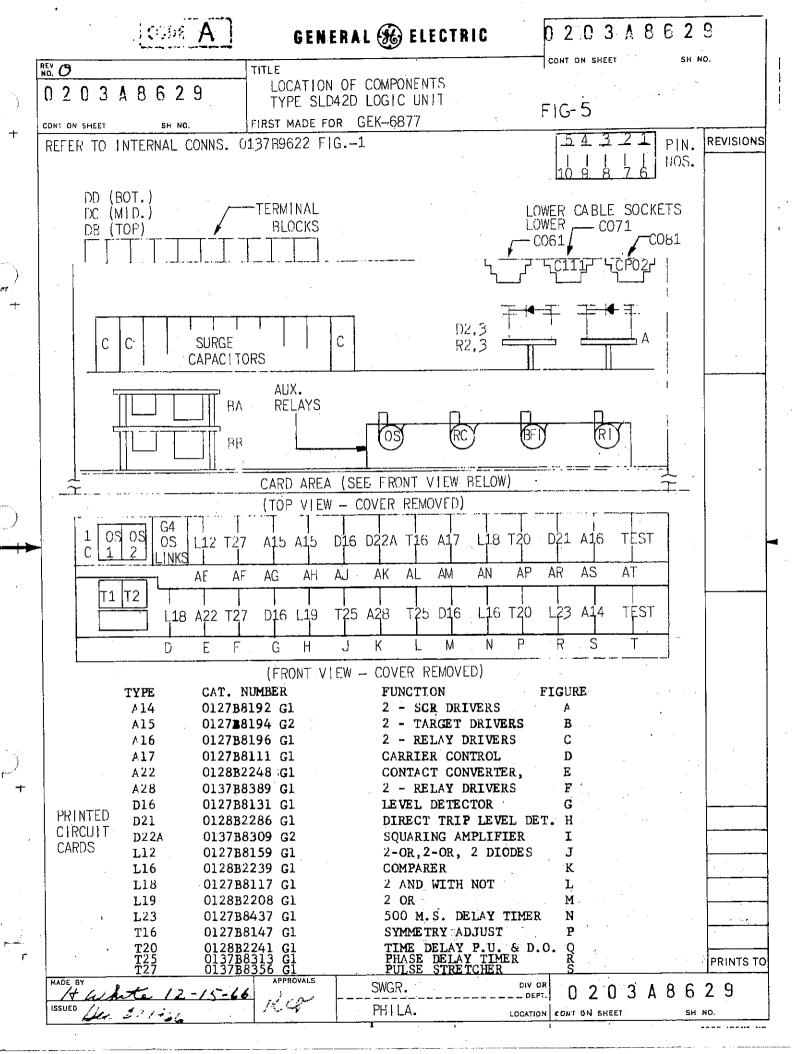

The Logic Unit is four rack units high and contains the various printed circuit cards to provide the functions listed above. All the output functions listed above (trip circuits and auxiliary relays) are located in the Logic Unit. The outline and mounting dimensions are shown in Fig. 4. The printed circuit cards plug in from the front of the unit into sockets which are keyed to prevent insertion into the improper socket. The letter addresses (AE, AF, etc. for the upper row, and D, E, F, etc. for the lower row) appear on the card guide in front of each socket. These addresses are shown on the component location drawing, Fig. 5, and the internal connection diagram, Fig. 14. The signal test points (TP2, TP3, etc.) shown on Fig. 14 are connected to instrument jacks on the Test cards in the AT and T positions. TP1 (top) thru TP10 (bottom) are located on the AT card. TP11 (top) thru TP20 (bottom) are located on the T card. The Logic Unit also includes a CHANNEL TRIP push button to simulate FDL and FDH output, and an INST. TRIP push button to simulate G4 output. A window in the front cover allows observation of the two SCR and two OS targets and the C (carrier) and I (instantaneous overcurrent) trip lamps. Both the targets and trip lamps are reset by push buttons in the window. Moveable links are provided behind the front cover to allow the G4 and RC circuits to be connected or disabled.

#### ASSOCIATED EQUIPMENT

The SLD42D requires a Type SSA D.C. power supply to supply regulated 17 V D.C. and bias to operate the logic and output circuits. A high speed carrier channel (Type CS26) is used with each SLD42D to transmit and receive signals proportional to line current phase angle, to obtain differential protection between remote ends of a protected line. A type SLYL12 distance relay is also used to obtain the required fault detector sensitivity on balanced three phase faults, where FDL and FDH (operated by negative sequence), may not respond.

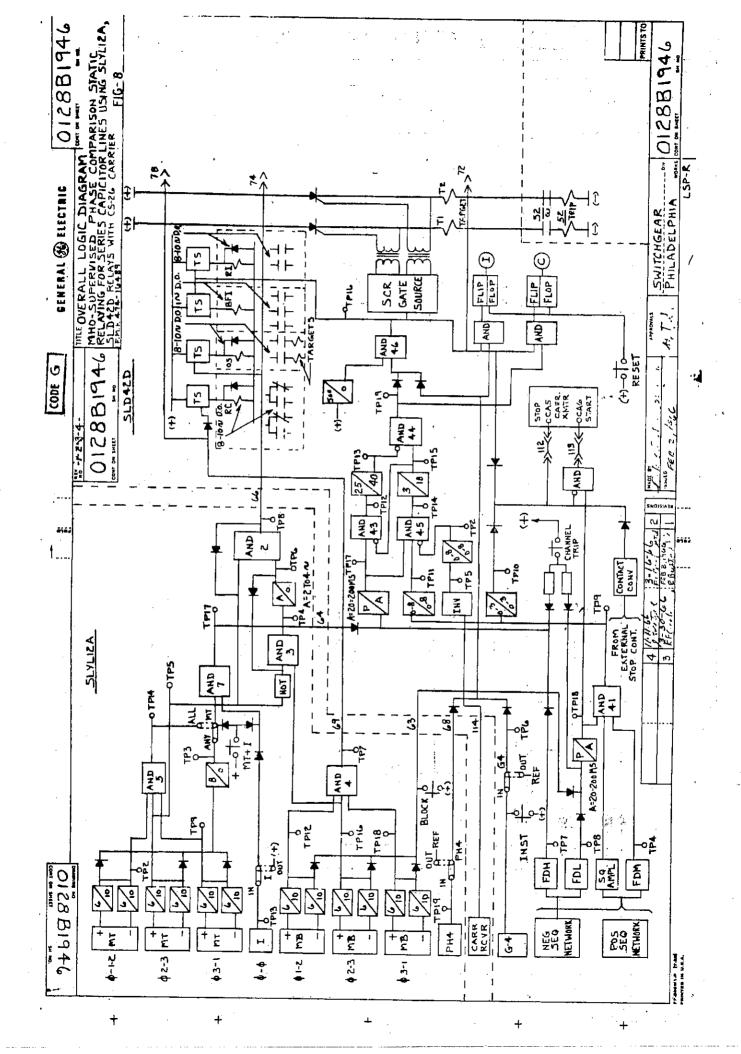

The signal interconnections between the SLD42D and the SLYL12, CS26, and SSA are provided by plug-in type multi-conductor shielded cables. These signal interconnections between the SLD42D, SLYL12, and CS26 are shown on the typical overall logic diagram of Fig. 8.

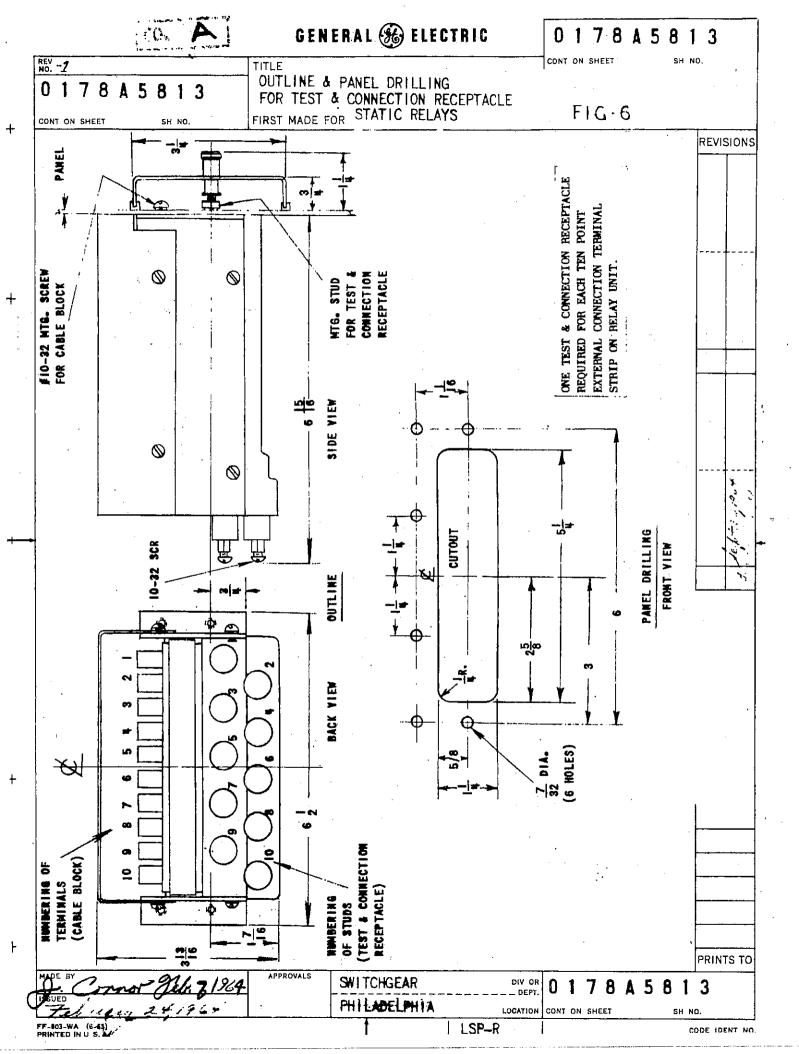

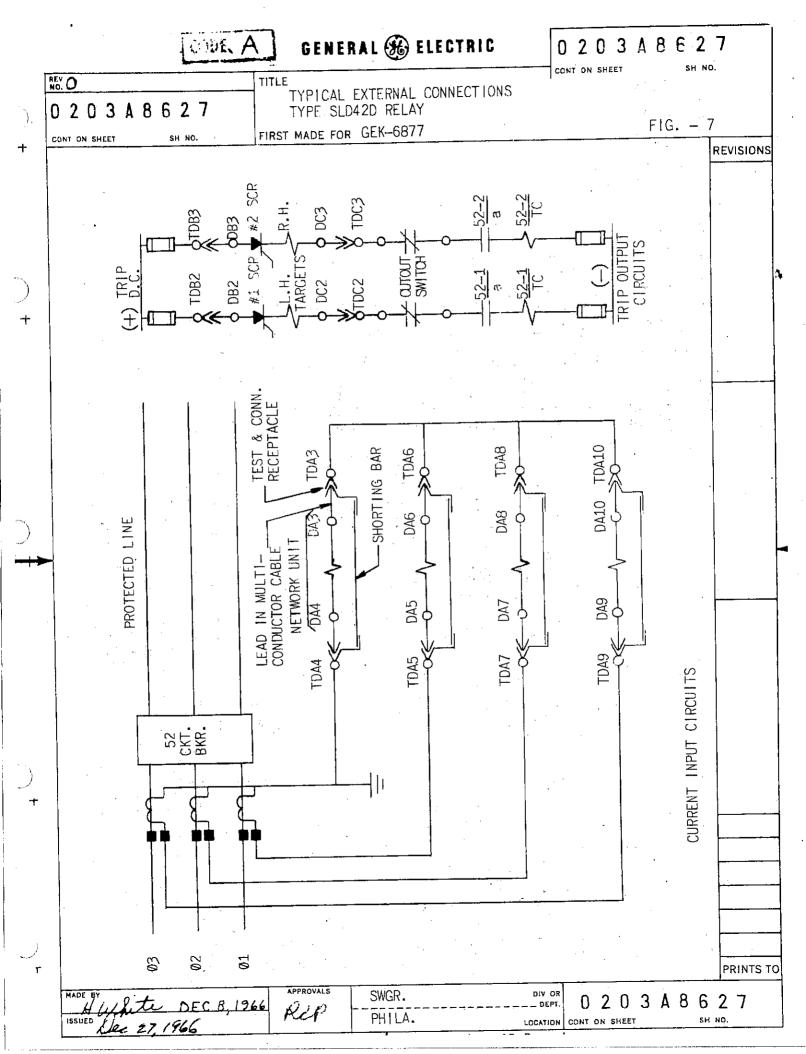

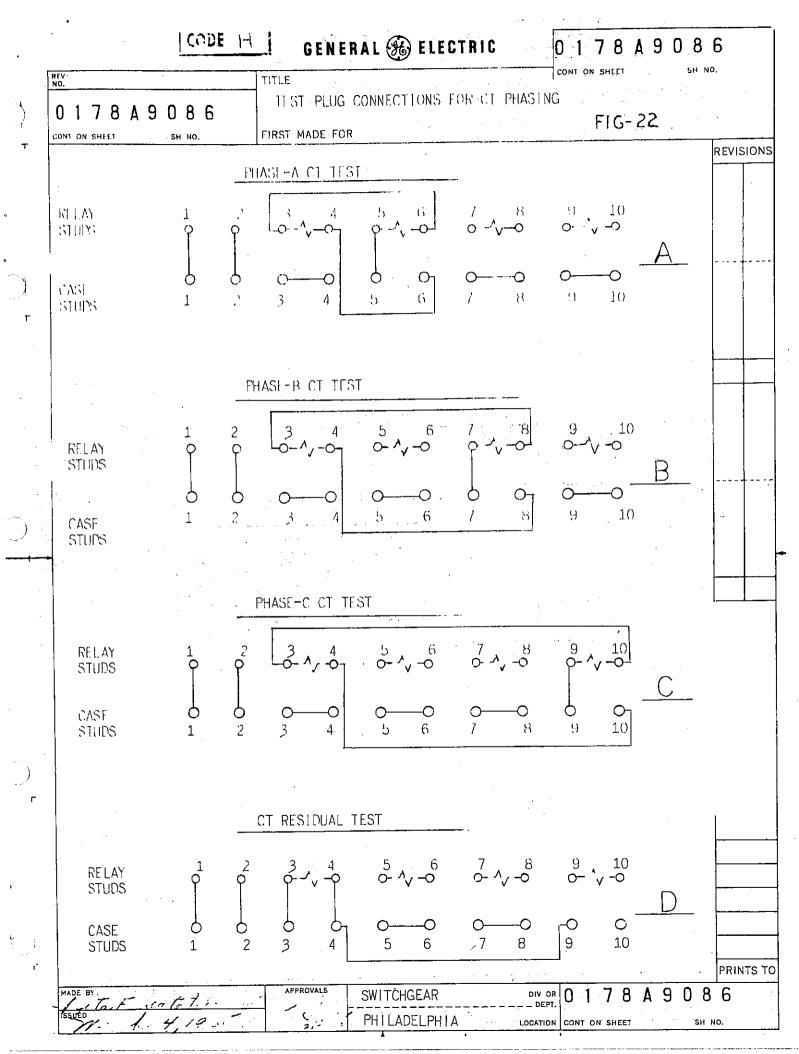

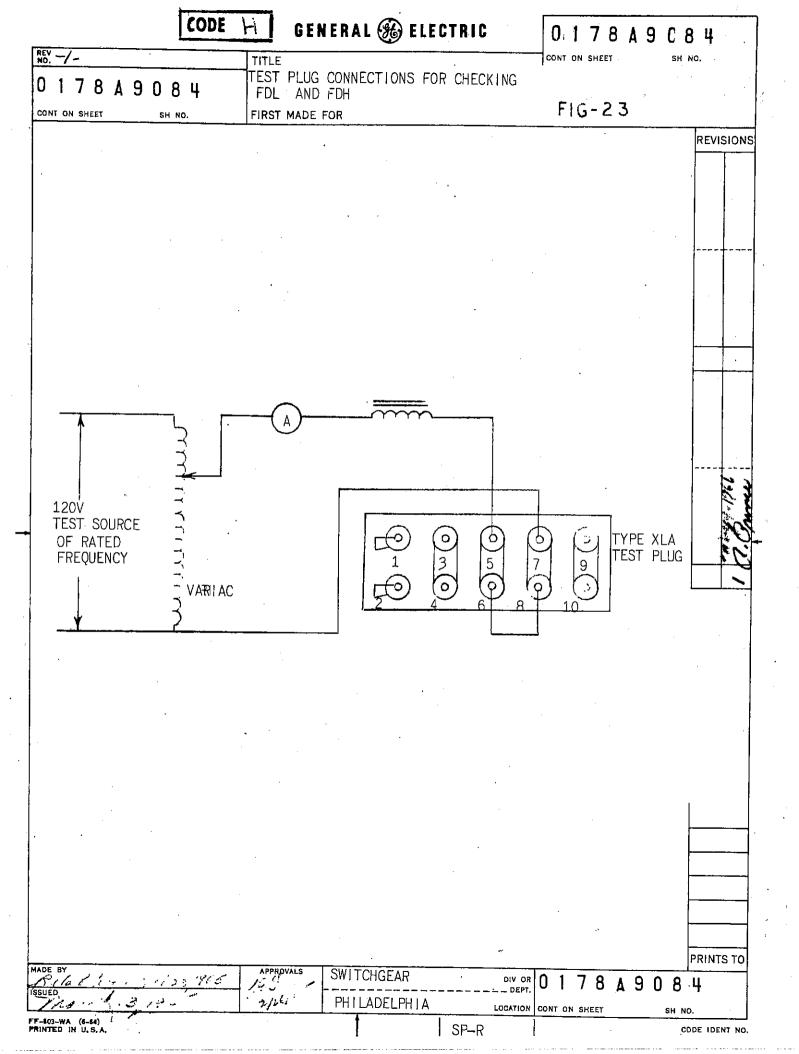

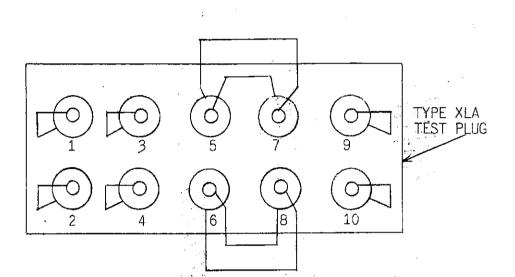

The incoming current connections to the SLD42D Network Unit from the C.T.s are made via a Test and Connection Receptacle, which is connected to the DA terminal strip on the unit by a 10-conductor cable. This Test and Connection Receptacle (shown in Fig. 6) allows disconnection from the C.T.s by removal of the connection plug, and A.C. testing with the standard Type XLA relay test plug. The various trip and auxiliary output circuits connected to the Logic Unit DB, DC, DD terminal strips are similarly connected to the external circuits via three additional Test and Connection Receptacles (TDB, TDC, TDD). A typical external connection diagram for the SLD42D is shown in Fig. 7.

#### RATINGS

#### TEMPERATURE

65° C maximum ambient outside the relay cases.

### **ELECTRICAL**

5 amp, 60 cycle continuous, and 250 amp, 60 cycle for one second for all input current circuits.

125 volts DC, 30 amp tripping duty on SLD42D1 trip circuits. 250 volts DC, 30 amp tripping duty on SLD42D2 trip circuit. 1 amp, DC targets on all series targets for OS and SCR. 0.5 amp inductive interrupting rating at 125 V DC all auxiliary relay contacts. 0.25 amp inductive interrupting rating at 250 V DC all auxiliary relay contacts. 3 amp DC continuous rating on all auxiliary relay contacts.

### BURDEN

10 volt-amperes maximum current burden per phase pair at 5 amp, 60 cycles.

#### ADJUSTMENT RANGES

FDL pickup = 0.2-1.6 amp. Neg. Sequence ( $I_2$ )

FDH pickup = 0.5-4 amp. Neg. Sequence ( $I_2$ )

K (Ratio of Neg. to Pos. Seq. Sensitivity) = 5/7/10FDM pickup = 0.2-0.6 amp. Neg. Sequence ( $I_1$  = 0)

FDM pickup = 0.2K-0.6K amp. Pos. Sequence ( $I_2$  = 0)

G4 pickup = 4-40 amp. residual (3Io)

FDL, FDH, FDM, and G4 are continuously adjustable over the above specified ranges by means of the adjusting screw on the front of the corresponding level detector cards. The selection of the K ratio is made by means of a tap block on the front of the Network Unit.

### OPERATING TIMES

Phase Comparison tripping time is 1 cycle maximum for all faults except balanced three phase faults. (Maximum tripping time for balanced three phase faults using SLYL12 supervising relay is 1 3/4 cycle.)

G4 direct tripping time on ground faults is 1/2 cycle maximum.

The pickup and dropout times of the auxiliary relays are shown in the following table:

| OPERATING TIM | (IN CYCLES) |

|---------------|-------------|

|---------------|-------------|

| AUX. RELAY | PICKUP | DROPOUT |

|------------|--------|---------|

| RI         | 1      | 8-10    |

| BFI        | 1      | 1       |

| RC         | 3/4    | 8-10    |

| os _       | 3/4    | 8-10    |

#### OPERATING PRINCIPLES

### PHASE COMPARISON

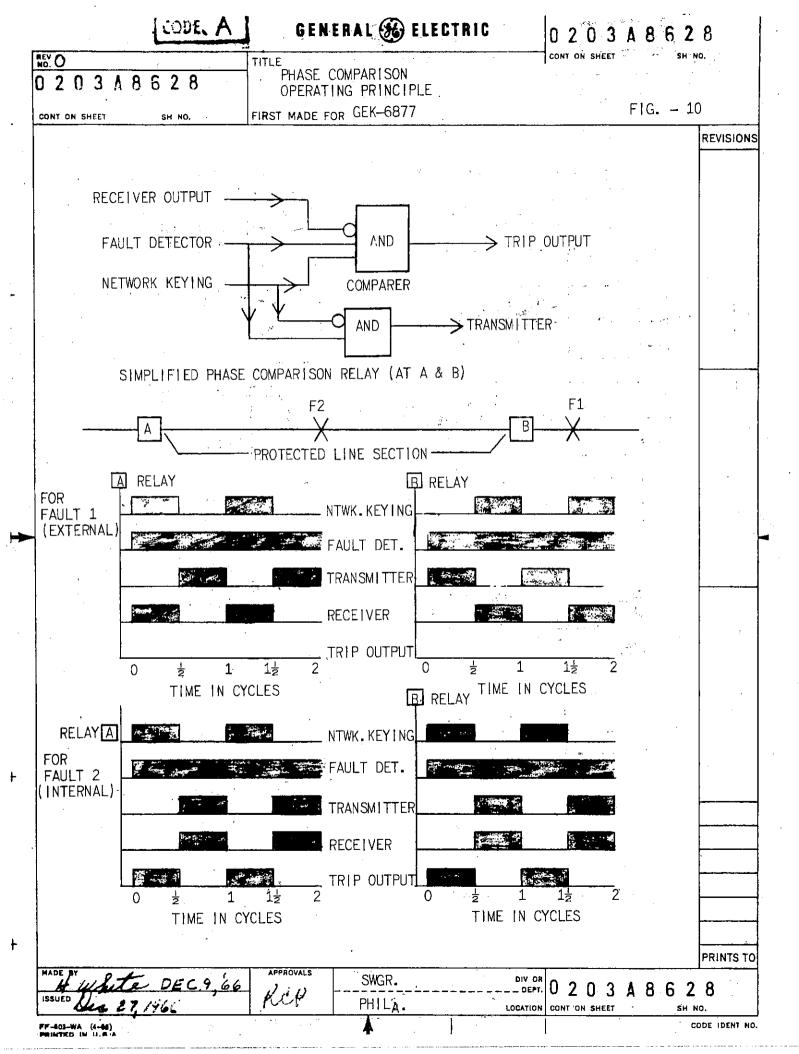

A phase-comparison pilot relaying scheme operates on the basic principle that a fault can be judged to be either internal or external to a protected line section by comparing the relative phase positions of the fault currents at the two ends of the line. In practice the quantities used in making the comparison between the two ends of the line are single-phase voltages which are obtained by combining the CT secondary currents at each end. The single-phase voltages are used to produce a square-wave signal which modulates the channel transmitter and attempts to trip the local breaker on alternate half-cycles. This basic operation of a phase comparison scheme is illustrated in Fig. 10.

In the SLD42D relays the single-phase voltage, which will be referred to as a "keying signal", is obtained by combining the outputs of a negative-sequence and a positive-sequence network with the resultant output weighted to favor the negative-sequence component by a multiplying factor "K". That is, the resultant keying signal is proportional to  $I_2 - \frac{I_1}{V}$ .

### NEGATIVE-SEQUENCE NETWORK

These positive and negative-sequence networks are contained in the Network Unit. The complete internal connections are shown in Figure 11. It will be noted that the postive- and negative-sequence networks are similar but differ in the way they are connected to the CT secondaries. Both networks consist of two transactors, each with two primary windings and an adjustable resistive load across a secondary winding. The positive-sequence network consists of transactors TE and TF with adjustment potentiometers P<sub>1</sub>, P<sub>2</sub> and P<sub>3</sub>. The negative-sequence network consists of transactors TG and TH with adjustment potentiometers P<sub>4</sub>, P<sub>5</sub>, and P<sub>6</sub>.

The term "transactor" is a contraction of transfer-reactor. It is essentially an air-gap current transformer with secondary current, and hence secondary voltage across the loading resistor, proportional to the vector sum of the input currents in the leading direction. The performance of a transactor in a circuit is described by its transfer impedance  $Z_T$  and the associated angle  $\theta_T$ :

$$Z_{T} = \frac{V_{out}}{I_{in}} \frac{\theta_{T}}{\theta_{T}}$$

(1)

Where:

Vout = Secondary output voltage

$I_{in}$  = Vector sum of the input currents

$\theta_{T}$  = Angle by which  $V_{out}$  leads  $I_{in}$ .

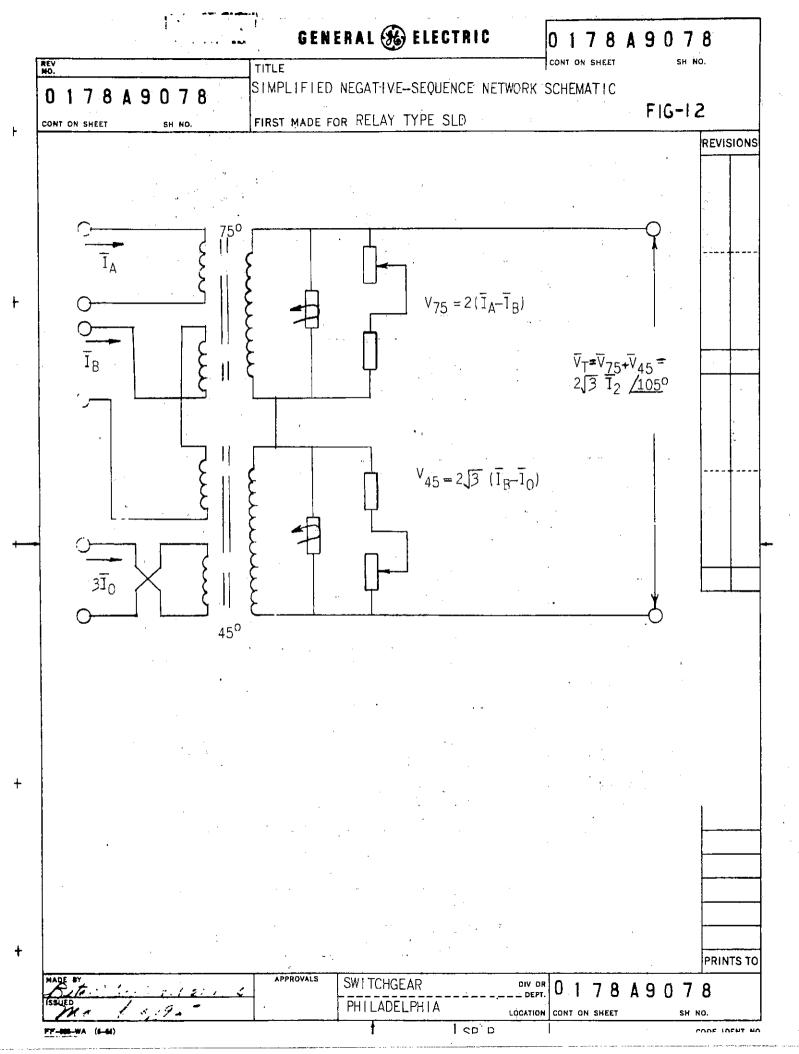

The negative-sequence network will be used to explain the operating principles of the sequence network in the SLD42D relay. This network is represented in simplified form in Figure 12. A negative-sequence network is, of course, one which produces an output proportional to the negative-sequence component of the input currents, and further produces no output for the positive- or zero-sequence components of the input current. It can be shown that using two transactors as in Figure 12 the output will be proportional only to negative-sequence current if the transactor angles are  $30^{\circ}$  apart and if the transactor with the lower angle has a transfer impedance higher than the other by a  $\sqrt{3}$  ratio. In the SLD negative-sequence network the angles are  $75^{\circ}$  and  $45^{\circ}$ , and the impedances are 2 and  $2\sqrt{3}$  ohms respectively.

As shown in Figure 12 the 75° transactor windings are connected to phase-A and reversed phase-B CT currents. The output voltage, therefore, is:

$$\overline{v}_{75} = 2 (\overline{I}_A - \overline{I}_B)$$

(2)

The  $45^{\circ}$  winding transactor is energized by phase-B CT current and reversed CT residual current (3Io), but since the residual winding has one-third the turns of the phase-B winding, the output voltage can be expressed by:

$$V_{45} = 2\sqrt{3} (I_B - I_o)$$

(3)

If the transactor secondaries are connected in series, as shown in Figure 12, the network output voltage  $V_{\mathrm{T}}$  can be expressed **as** follows:

$$\overline{V}_{T} = \overline{V}_{75} + \overline{V}_{45} = 2(\overline{I}_{A} - \overline{I}_{B}) / 75^{\circ} + 2\sqrt{3}(\overline{I}_{B} - \overline{I}_{o}) / 45^{\circ}$$

(4)

It can be shown that this network output voltage is proportional to the negative-sequence component of the input currents. That is:

$$\overline{V}_T = 2\sqrt{3} I_2 / 105^{\circ}$$

Where I is phase-A (5)

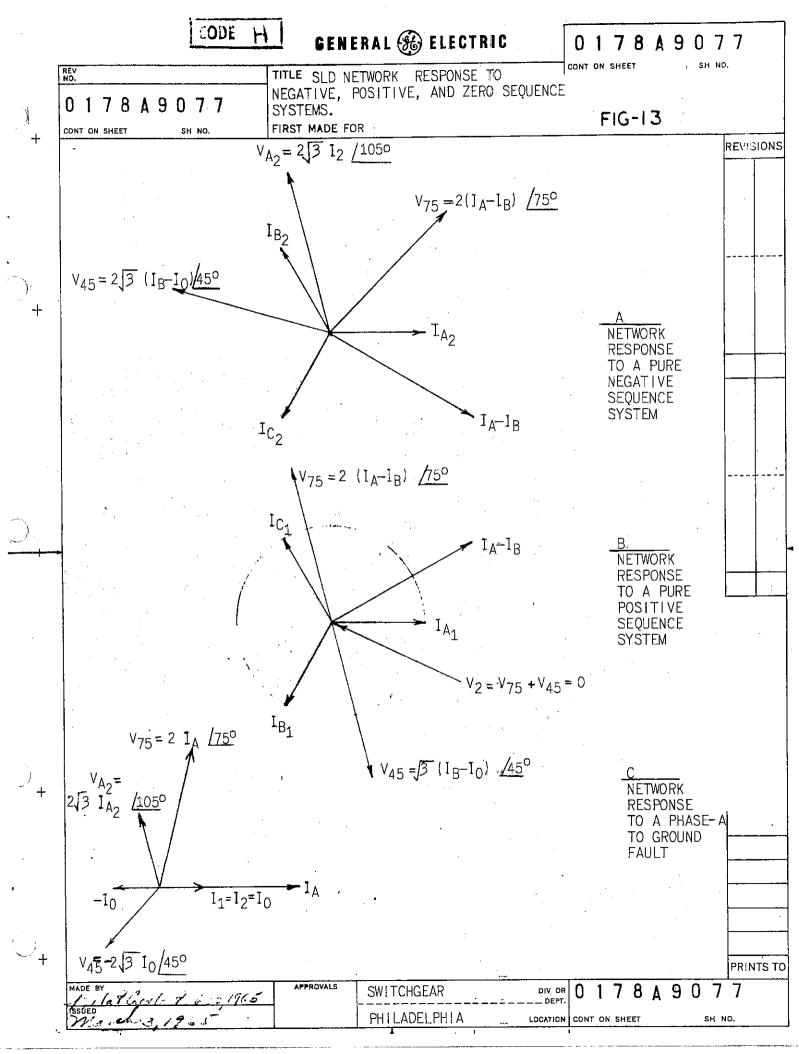

This relationship can best be shown graphically. Figure 13A shows that for a pure positive-sequence system the magnitudes and angles of the transactor secondary voltages are such that the voltages are equal and  $180^{\circ}$  apart. Thus the secondary voltages cancel and the network output  $V_{T}$  is zero.

Figure 13B shows the response of the network to a three-phase system of pure negative-sequence currents. Note that the network output voltage is now equal to  $2\sqrt{3}$  I<sub>2</sub>  $/105^{\circ}$ , with the angle referenced on the phase-A current, i.e., I<sub>A2</sub>. This agrees with equation (5) above.

Figure 13C shows the response of the network to a phase-A to ground fault. Here we see that the zero-phase sequence component of the fault current has been eliminated from the network response by the action of the  $I_o$  winding of the  $45^o$  transactor, and that the network output voltage is again  $2\sqrt{3}$   $I_2$   $105^o$ .

### POSITIVE-SEQUENCE NETWORK

It can be shown that a positive-sequence network can be obtained by means of the same components used in the negative-sequence network described

above, provided only that the phase-C current is used instead of phase-B. That is:

$$\overline{\mathbf{v}}_{\mathrm{T}} = \frac{2}{3}(\overline{\mathbf{I}}_{\mathrm{A}} - \overline{\mathbf{I}}_{\mathrm{C}}) \frac{\sqrt{75^{\circ}} + 2\sqrt{3}(\overline{\mathbf{I}}_{\mathrm{C}} - \overline{\mathbf{I}}_{\mathrm{o}}) \frac{\sqrt{45^{\circ}}}{45^{\circ}}$$

(6)

$$\overline{V} = \frac{2}{3}\sqrt{3} \overline{I}_{A1} / 105^{\circ}$$

(7)

This can be demonstrated by a graphical analysis similar to that used for the negative-sequence network. The 1/3 factor in equations (6) and (7) results from the use of 1/3 as many primary turns in the positive-sequence transactors.

It should be emphasized that the 105° angle which appears in equations (5) and (7) above results from calculations based on the open circuit condition of the network. In practice the loading effect of the low-pass filter will cause the angle of the network output voltage to deviate from the 105° calculated value, but since the loading will be practically the same in the network units as the two ends of the line, the angles will also be the same.

It should be noted also that the choice of  $75^{\circ}$  and  $45^{\circ}$  for the transactor angles is one of practicality rather than necessity. The only requirement in the basic design is the  $30^{\circ}$  difference between the two angles and the  $\sqrt{3}$  relation between the transfer impedances. It is important, however, that the angles be the same from network to network to insure coordination between terminals.

### LOGIC CIRCUITS

The operation of the logic circuits are best explained by referring to the Logic Unit Internal Connection Diagram, Fig. 14. AND 45 (N) is the comparer previously described. The keying input signal at TP11 is obtained from the mixed (positive and negative sequence) network output which has been passed through the squaring amplifier (AK). The squared keying signal is supervised by the FDM keying level fault detector (G) and the FDL blocking level fault detector (AJ) at AND 41 (AK). The FDH tripping level fault detector (M) output is supplied to the comparer at TP17. Both FDL and FDH operate on negative-sequence voltage from the Network Unit to obtain maximum sensitivity on unbalanced faults, while remaining insensitive to balanced load currents. The FDL and FDH functions on balanced three-phase faults are provided by the lens-type MB and MT function in the associated type SLYL12 distance relay. These signals are connected into the Logic Unit via shielded cable pins 63 and 64. The pulse stretchers (F) and (AF) are present to provide a continuous output for cases where the apparent impedance seen by the SLYL12 MB and MT functions immediately after fault inception may not allow a continuous signal.

In the previous discussion of phase-comparison operation (and in Fig. 10) it was shown that the keying signal must operate the transmitter during the half cycles which the comparer is not being energized. This is accomplished by the application of a continuous "start" signal to the channel control card (AM) at TP18 when FDL operates, and applying the squared keying signal from TP9 to the channel control "stop" input. The key-off signal is passed through the symmetry card (AL) to allow adjustment of the carrier on-off times to achieve a symmetrical receiver output at remote terminal. This unsymmetrical transmitter modulation is necessary to compensate for differences in the turn-on and turn-off of the remote receiver.

The local receiver output is connected to the NOT input to the comparer via an inverter and an 0-8/0-8 card (L). This 0-8/0-8 (L) provides an integrating time on received carrier to avoid possible incorrect blocking due to momentary bursts of carrier on gap flashover during an internal fault. The phase delay (J) card is present to compensate for channel delay and the carrier integrator (L) and provide the optimum relation between the comparer keying input and the comparer blocking input. The receiver output is passed through the inverter (N) to provide signal compatibility between the positive referenced CS26 carrier and the negative referenced SLD42D logic. A similar signal inversion occurs in the CS26 transmitter control at the SLD42D channel control interface.

An external fault above FDH pick up level does not produce a comparer output because half cycle blocking signals are present at TP2 in phase with the TP11 keying signal. An internal fault above the FDH pickup level will produce comparer output at TP14 on the half cycles corresponding to TP11 keying, since the TP2 comparer blocking signal will not be present during that half cycle. The comparer output is passed through the trip integrator (P) to provide a continuous signal to the trip bus at the TP16 via AND 44 and AND 46.

AND 44 provides supervision of the trip integrator (P) output by the RB transient blocking function. The RB function consists of AND 43 (AN) plus the 25/40 timer (AP). If a system fault occurs, operating FDH, and there is no trip integrator output within 25 milliseconds, an RB output will be produced at TP13. This RB output will block AND 44 until 40 milliseconds after the fault is cleared and FDH drops out. Since the RB pickup time is longer than the maximum tripping time for internal faults, the RB blocking function can only get set up on external faults. For internal faults the trip integrator output at TP15 will block AND 43 and prevent the 25/40 timer from timing and blocking tripping at AND 44. In this way the RB function acts to block any tripping until about 2 1/2 cycles after an external fault is cleared.

AND 46 (R) provides 500 timer supervision of all tripping signals. The purpose of this 500 timer supervision is to prevent a trip output at the TP16 trip bus until the DC supply to the equipment has been energized for approximately one-half second. This eliminates the possibility of undesired trips when the DC is initially switched on.

The G4 direct trip overcurrent function (AR) is operated from the output of the TD residual current ( $3I_0$ ) transactor in the Network Unit. The G4 output at TP6 is passed through an OR circuit (H) and through an OR input to the AND 46 500 timer supervision to the trip bus at TP16. The other (H) OR input is connected to PH4 direct trip phase overcurrent function in the associated SLYL12 relay.

A contact converter circuit is provided to stop all carrier by closing an external normally-open contact. The output of this contact converter (E) is connected directly to a second OR input to the channel control (AM) "stop". The third OR input to the "stop" portion of the channel control card is connected to the TP16 trip bus. Any of the three "stop" inputs to the channel control card has preference over the "start" input.

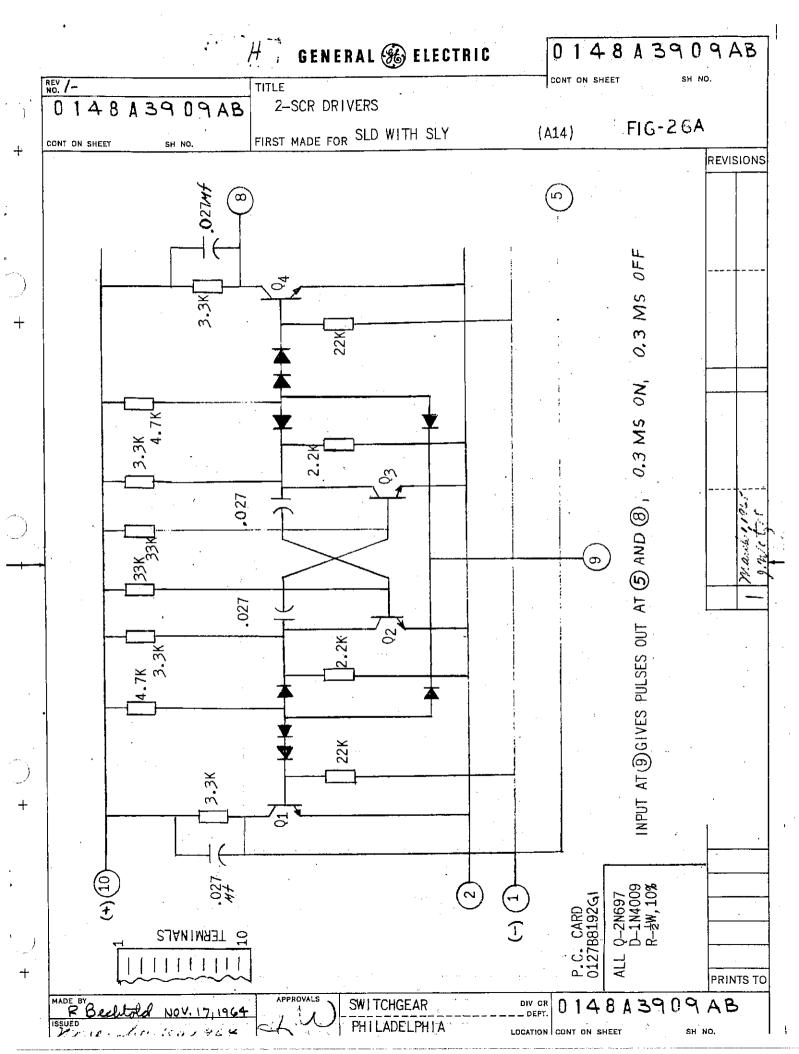

#### OUTPUT CIRCUITS

A signal of the trip bus at TP16 produces a series of pulses from the SCR driver (S). These pulses are connected to the tripping SCR gate circuits by isolating transformers on sub-assemblies BA and BB. The anodecathode junction of the SCR will conduct during the gating pulse interval, and will remain in the conductive state as long as the external circuit is completed and continues to draw current through the anode-cathode junction. This loss of gate control once the SCR is "fired" provides an effective "seal-in" on the trip circuit. It also means that the SCR trip circuit must be interrupted by an auxiliary contact on the breaker which will open when the breaker has been tripped. A hand-reset electromechanical target is connected in series with each SCR trip circuit.

The C (carrier) target lamp is turned on by the presence of TP16 trip bus signal and a TP19 (phase comparison trip) signal at AND 47 (AN). The I (instantaneous overcurrent) target lamp is turned on by the presence of a TP16 trip bus signal and a G4 or PH4 signal from the OR circuit on the (H) card. These C and I lights will remain on until the reset button is operated.

The BFI and RI auxiliary telephone-type relays are operated by the presence of a TP16 trip bus signal at the drivers (AS). The RC relay is operated via the upper relay driver on the (K) card by a three-phase SLYL12 fault detector (ALL MB) signal, or the optional time-delayed trip circuits (if used). If these SLYL12 circuits are used, the RC function will provide a contact output to cancel reclosing for three-phase faults or second zone faults. The lower relay driver (K) operates the OS relay for an out-of-step signal from the SLYL12. The 8-10 cycle time delay drop out time on RI, RC, and OS is obtained by diodes on their respective driver cards which are connected in parallel with the relay coils.

The detailed operation of the individual logic functions (AND, NOT, etc.,) may be understood by referring to the various card internal connection diagrams shown in Fig. 26A-26S.

### APPLICATION

#### GENERAL

The Type SLD42D phase comparison relays (in conjunction with the SLYL12A) are particularly adapted to the protection of lines where the presence of mutual induction with split busses, or series capacitor compensation, makes the application of directional comparison relaying difficult or unreliable.

The SLD42D relay uses mixed positive plus negative sequence excitation. As explained previously, this is accomplished by passing the three phases of the CT secondary current through a positive and then a negative sequence filter. A portion of the single-phase output of the positive-sequence filter is then vectorially subtracted from the full single-phase output of the negative sequence filter to yield a single-phase quantity that is proportional to:

$$I_{K} = I_{2} - \frac{I_{1}}{K}$$

(8)

where K can be set for 5, 7, or 10. The phase angle of this quantity is compared with the phase angle of a similarly obtained quantity at the remote end of the line, if the negative sequence fault detectors FDL and FDH (or distance fault detectors) and the signal magnitude detector FDM, operate on an internal or external fault.

The basic idea behind the mixed excitation is to have the negative sequence ( $I_2$ ) swamp out the positive sequence ( $I_1/K$ ) for all faults except three-phase faults so that for all unbalanced faults the phase comparison will essentially be on a negative sequence basis. For three-phase faults, there will be no negative sequence current (except that which results from unbalances introduced by such things as non-transposition of lines, current transformer saturation, or load unbalance) so the phase comparison will be on a positive sequence basis. It is important to recognize that, neglecting load current, I1 and I2 in equation (8) above, will be equal to each other for phase-to-ground faults. For double phase-to-ground faults, I1 will always be greater than I2 by an amount that depends on the ratio of the system zero sequence to positive sequence impedance. For this reason, it is necessary to consider double phase-to-ground faults as well as single-phase-to-ground faults in the application of the SLD42D relay. For a given fault location, the negative-sequence component of current for a phase-to-phase fault will always be half of the three-phase positive-sequence fault current and eqaul to, or greater than, the negative sequence component in a double-phase-toground fault, so there is no need to consider phase-to-phase faults separately.

Where the SLD42D relay is applied to long, heavily loaded HV or EHV transmission lines with series capacitor compensation, the influence of load current, shunt capacitance, shunt reactors, and series capacitors requires more detailed consideration for optimum reliability than would be the case for short lines.

### LOAD CURRENT

For an internal fault, the carrier signals illustrated in Figure 10 assume that the load current is negligible and therefore, the received carrier

is in phase with the transmitted carrier. The presence of a substantial load current, which continues to flow through the line during an internal fault, may cause the keying signals at the two ends to be shifted out of phase; thereby increasing the time that carrier is received beyond one half cycle, and reducing the carrier off time below one half cycle. Tripping is obtained if the duration of the carrier received signal is less than  $300^{\circ}$ . Reliable tripping is assured if the phase angle between the keying signals at each terminal is limited to no more than  $60^{\circ}$ .

The optimum value of K in equation (8) is the smallest value that will restrict the phase angle between keying signals on unbalanced faults to  $60^{\circ}$ , thereby assuring maximum sensitivity on 30 faults.

$I_1$  of equation (8) is the sum (by superposition) of the prefault load and the fault component determined by Thevenin's theorem. The influence of load current on equation (8) is most readily obtained by evaluating the keying signal resulting from fault components of current  $I_{KF}$  and comparing it with the keying signal resulting from the load component of  $I_1$ ,  $I_{KL}$ .

Equation (8) can be rewritten:

$$I_K = I_{KF} - I_{KL} = (I_2 - I_{1F}) - I_{1L}$$

(9)

On the assumption that the positive source impedance is equal to the negative source impedance, and the sources at both ends of the line have the same impedance angle,  $I_{KF}$  will have the same phase angle at both terminals.  $I_{KL}$  may be assumed equal in magnitude at both terminals and opposite in polarity.

It is assumed that  $I_{KL}$  may have any phase relationship to  $I_{KF}$ , the worst angle being a function of the negative (and positive) distribution factor (C) as illustrated in Figure 15. The method of selecting the optimum value of K is covered under the calculation of settings.

#### SHUNT CAPACITANCE

The current flowing into the shunt capacitance during an external fault will cause the sequence currents seen at the two terminals to be dissimilar. The negative sequence fault detectors FDH and FDL have a difference in setting larger than the negative sequence current flowing in the shunt capacitance to assure that the tripping element FDH is not picked up at one end before the carrier start element FDL is energized at the other.

A further consideration is that the keying signal  $I_{KF}$  may be larger at one terminal than it is at the other for an external fault. If  $I_{KL}$  is opposite in polarity and equal in magnitude to the mean of  $I_{KF}$  at the two terminals the keying signals  $I_{K}$  would have opposite polarity at the two terminals. FDM should be set to preclude keying at one terminal for this condition.

The inrush into the shunt capacitance on line energization, particularly with unequal pole closing of the breaker, may limit the setting of FDH that can be safely used.

The current drawn by the shunt reactors, if connected in the protected zone will reduce the steady state charging current of the shunt capacitance seen by the relays, but may not reduce the transient inrush on line energization.

#### SERIES CAPACITANCE

The series capacitance may affect the phase comparison indirectly if spurious carrier is generated when the protective gaps flashover. It is anticipated that these bursts of spurious carrier will be in the order of one millisecond duration which could reset the phase comparator timer if allowed to block AND 45 (Ref. Fig. 14). An integrating timer is employed ahead of AND 45 with an adjustable on and off delay. The factory setting of 2 ms/2 ms will preclude resetting on the 1 ms burst of carrier.

The low frequency transient component of fault current associated with series capacitors may cause intermittent operation of the fault detectors. The transient blocking circuit input (AND 43 Fig. 14) and the phase comparison circuit supervision input (AND 45 Fig. 14) are maintained by timer P/A for a preselected time, assuring continuous phase comparison regardless of the resetting of fault detectors. To assure coordination, the carrier start signal must be sealed in by a second P/A timer with a reset delay set longer than the P/A timer on the trip supervision.

### INFORMATION REQUIRED FOR SETTING CALCULATIONS

In order to establish the optimum settings for the SLD42D relay, it is necessary to obtain the following system data:

- 1. Maximum load current that will flow in the line for each system configuration to be considered.

- 2. Minimum positive sequence fault current that will flow in each terminal for internal three phase faults near each terminal and the midpoint of the line for each system configuration.

- 3. Minimum positive and negative sequence fault current that will flow in each terminal for single line to ground faults near the midpoint of the line and near each terminal for each system configuration.

- 4. Minimum positive and negative sequence fault current that will flow in each terminal for double line to ground faults near each of the terminals for each system configuration.

- The ratio  $\rm R_{\rm O}$  (ØG) of  $\rm I_{\rm O}$  for single line to ground faults to  $\rm I_{\rm 30}$ for 3 phase faults for each fault location and each system configuration.

If the information is not available directly in the form required, it can be derived if the fault study provides for each location:

- 1. The total 3 phase fault current and the distribution factors.

- The total zero sequence fault current for a single line to ground fault.

#### 3. The maximum load current.

The total negative sequence fault current for single line to ground fault ( $I_{2(\emptyset G)}$ ) will be equal to  $I_{o}$ , as will the total fault component of the positive sequence current ( $I_{1F(\emptyset G)}$ ).

The ratio  $R_O(\emptyset G)$  may be used to obtain the positive  $(I_{\mathrm{IF}}(\emptyset \emptyset G))$  and negative  $(I_2(\emptyset G))$  sequence components of fault current for double line to ground faults in conjunction with  $I_3\emptyset$  at the same fault location.

$$I_{1F}(\emptyset \emptyset G) = R_{1}(\emptyset \emptyset G)$$

$I_{3\emptyset} = I_{3\emptyset}$   $\frac{1-R_{o}(\emptyset G)}{2-3R_{o}(\emptyset G)}$

R<sub>1(00G)</sub> can be read directly from Fig. 16A

$$I_{2}(\emptyset G) = R_{2}(\emptyset G)$$

$I_{3\emptyset} = I_{3\emptyset} \frac{1-2R_{O}(\emptyset G)}{2-3R_{O}(\emptyset G)}$

R2(00G) can be read directly from Fig. 16B

The distribution of negative and positive sequence components of fault current at terminals X and Y can be obtained by multiplying the total sequence components of fault current by the distribution factors  $C_X$  and  $C_{Y^{\bullet}}$ .

### CALCULATION OF SETTINGS

The installation adjustments of the SLD42D consist of the pickup settings of G4, FDH, FDL, FDM, and the value of K which determines the relative emphasis on the positive and negative sequence inputs to the keying signals. The settings will be discussed in the sequence in which they will be calculated. A sample calculation is made for the system in Figure 17A, which is presumed to provide for the protected line the most onerous application from a consideration of load studies and equipment outages.

Figure 17B illustrates the tabulation of data for the sample system.

The load current  $I_{1L}$  is obtained from load flow studies for the system configuration under study.

I30 is the total 3 phase fault current at the fault location.

$I_0$  is the total zero sequence current for a single line to ground fault at the fault location.  $R_{O}(g_{\rm C})$  is the ratio of  $I_0/I_{36}$ .

$C_{\rm x}$  and  $C_{\rm y}$  are the positive sequence distribution factors for the fault location, and are assumed equal to the negative sequence distribution factors.

Before calculating  $I_{2(\emptyset G)_X}$ , which is equal to  $I_{2(\emptyset G)C_X}$ ,  $R_{O(\emptyset G)}$  should be evaluated to ascertain if the lowest negative sequence current is associated with single line to ground faults or double line to ground faults. If  $R_{O(\emptyset G)}$  is .333 or lower,  $I_{2(\emptyset G)}$  will be equal or lower than  $I_{2(\emptyset G)}$ , and  $I_{2(\emptyset G)}$  should be calculated. Conversely, if  $R_{O(\emptyset G)}$  is larger than .333,  $I_{2(\emptyset G)}$  will be smaller, and should be calculated.

### PICKUP SETTINGS OF FDH AND FDL

To provide coordination between the fault detectors at the two terminals, the setting of FDH at one terminal should be at least 4/3 the setting of the FDL at the other terminal. If the negative sequence current in the shunt capacitance of the line is significant, then the setting of FDH should be increased so that:

$$FDH = I_{2SC} + 4/3 FDL$$

where  $I_{2SC}$  is the negative sequence current in the shunt capacitance (or the net shunt current if shunt reactors used) for a fault at the line terminals with minimum  $I_2$  flowing through the line.

I<sub>2SC</sub> may be calculated by first obtaining the minimum I<sub>2</sub> for fault locations, F1 or F3, Fig. 17A. The negative sequence voltage V2 at that fault location would be  $V_{\rm LN}$  multiplied by  $R_{\rm O}(\emptyset G)$  if  $I_{\rm 2}(\emptyset G)$  is less than  $I_{\rm 2}(\emptyset G)$ . If  $I_{\rm 2}(\emptyset G)$  is smaller than  $I_{\rm 2}(\emptyset G)$ , multiply  $V_{\rm LN}$  by  $R_{\rm 2}(\emptyset G)$ .

The average negative sequence voltage on the line

$$(V_{2AV}) = V_2 - I_2 \quad (C_x) \quad \underline{ZL}$$

For fault location F3 or  $(V_{2AV}) = V_2 - I_2 \quad (C_y) \quad \underline{ZL}$  For fault location F1

$$\begin{array}{rcl}

\mathbf{I}_{2SC} &= \mathbf{V}_{2AV} \\

& & \overline{\mathbf{Z}_{SC}(\mathbf{Z}_{SR})} \\

& & \overline{\mathbf{Z}_{SC}} + \mathbf{Z}_{SR}

\end{array}$$

where  $Z_{SC}$  is the total impedance of the shunt capacitance.  $Z_{SR}$  is the total impedance of the shunt reactors.

A further restriction of FDH is that it should be no more than 2/3 of the minimum  $I_2$  at the terminal considered for an internal fault.

A possible restriction on FDL is that it should be set above the negative sequence current that may result from maximum load current flowing through an untransposed line, otherwise continuous carrier may be transmitted.

Because the system represents a long line, FDH is set equal to 2/3 I<sub>2</sub> minimum to minimize the possibility of FDH picking up on line inrush.

#### SELECTION OF K FACTOR

As noted under general comments, the minimum value of K should be selected. For less onerous applications, K=5 should be selected. K=5 may be used with an ample margin of safety if the maximum load current is less than 125% of the smallest of  $I_2(\emptyset G)^x$ ,  $I_2(\emptyset G)^y$ ,  $I_2(\emptyset G)^x$ , and  $I_2(\emptyset G)^y$ . If this

relationship is not true, a more rigorous evaluation of the optimum value of K is necessary and the tabulation in Fig. 17B should be completed.

The curves in Figures 18A, B and C are provided to allow the selection of the K factor directly, utilizing the data tabulated in Fig. 17B. The curves are based on the following:

- 1. The angle between the keying signals at the two terminals should be no more than  $60^{\circ}$ .

- 2. A safety margin is obtained by using only 75% of the calculated negative sequence current.

With reference to Figure 18A, each fault location is checked by plotting the ratio of 30 fault current to load current,  $I_{30}/I_{11}$ , and the lower of  $C_{\rm X}$  and  $C_{\rm Y}$ . If the point is at the upper right of the top one of the parallel curves, K=5 will be suitable for that fault location.

If the point falls between the top and the bottom curve, enter the graph at the proper point on the  $R_{O(OG)}$  scale at the top of the graph, proceed down until the V curve is reached, then horizontally to the left, until the distribution factor C=.03 is intersected. Draw a curve parallel to the existing curves which passes through the intersection of the horizontal line drawn and C=.03. This construction is shown in dashed lines for two arbitrary values of  $R_{O}(OG)$ , one where OG is limiting, and one where OG is limiting. If the point  $C_{X}$  (or  $C_{Y}$ ) and  $C_{Y}$  and  $C_{Y}$  and  $C_{Y}$  above and to the right of the curve constructed for the specific value of  $C_{Y}$ 000, then  $C_{Y}$ 111 be satisfactory. If it plots below this curve then the procedure must be repeated, starting with Figures 18B, for  $C_{Y}$ 12.

If the initial plot of C and  $I_{30}/I_{1L}$  lies below and to the left of the bottom curve then K=5 is not suitable, and the procedure must be repeated, starting with Figure 18B for K=7.

If the procedure is repeated for K=7, and K=7 is found unsuitable, then proceed to Figure 18C for K=10.

When the value of K has been found for all fault conditions that may provide the limiting case, select the largest value of K (5, 7, or 10) and apply at both terminals. Different values of K at the terminals could result in a phase shift between the keying signals at each terminal for an unbalanced external fault, with false tripping as a possible consequence.

If desired, the angular displacement between the keying signals may be obtained by plotting a phasor diagram representing the 2 keying currents produced by the selected value of K.

Figure 19A illustrates the phasor diagram for the fault at F3, where the  $\emptyset G$  fault is the limiting condition.  $I_K$  is obtained at terminal x by first plotting .75  $I_{2}(\emptyset G)^{\times}$  to an appropriate scale. The positive sequence

component of the fault at x,  $I_{1F}(\emptyset G)_X$ , will be equal to  $I_2(\emptyset G)_X$ . Since the worst case of a phase A to G is assumed,  $I_{1F}(\emptyset G)_X/K$  is subtracted directly from .75  $I_2(\emptyset G)$  to give  $I_{KF}$ . From Fig. 15, the worst angle between  $I_{KL}$  and  $I_{KF}$  can be obtained for the lower value of C  $(C_X)$ . At this angle,  $I_{KL}$  is drawn to the same scale as  $I_2(\emptyset G)_X$  and the angle  $(\theta_1)$  between  $I_K$  and  $I_{KF}$  is obtained by measurement.

Similarly at terminal Y, 0.75  $I_2(\emptyset_G)_Y$  can be plotted (to a different scale if desirable) and  $I_{1F}(\emptyset_G)_Y/K$  can be subtracted directly from it to obtain  $I_{KF}$ .  $I_{KL}$  (to the same scale as  $I_2(\emptyset_G)_Y$ ) can be added to it  $180^\circ$  out of phase with  $I_{KL}$  at terminal X, to obtain  $I_K$ . The angle between  $I_{KF}$  and  $I_K$  at Y  $(\theta_2)$  is added to  $(\theta_1)$  to obtain the total angular displacement between the keying signals at the two terminals.

The angular displacement between the keying signals at the two terminals can be plotted in a similar manner for a case where a  $\emptyset \emptyset G$  fault is the limiting type of fault, with two exceptions.  $I_{1F}(\emptyset \emptyset G)_X$  is not equal to  $I_{2(\emptyset \emptyset G)_X}$  and must be obtained from the tabulation in Fig. 17B.  $I_{1F}(\emptyset \emptyset G)_X$  will not subtract directly from  $I_{2(\emptyset \emptyset G)_X}$  in the worst type of fault, but at  $60^{\circ}$ . The fault at location Fl is plotted in Fig. 20A.

### SETTING OF FDM

On some external faults, the fault component of the keying signal,  $I_{KF}$  may be approximately equal in magnitude, and opposite in polarity, to the load component of the keying signal,  $I_{KL}$ . In this event, the net keying signal  $I_{K}$  will approach zero, and the sequence current flowing in the shunt capacitance may cause  $I_{K}$  at one terminal to be  $180^{\circ}$  out of phase with  $I_{K}$  at the other terminal. To preclude keying at one, or both, ends for this possible condition, FDM should be set above 50% of the keying signal, produced by the positive and negative sequence charging currents.

$$FDM = \frac{V_2 \text{ (AV)}}{Z \text{ shunt}} + \frac{V_1 \text{ (AV)}}{KZ \text{ shunt}}$$

or

$$\frac{V_2 \text{ (AV)}}{Z \text{ shunt}} + \frac{V_{LN} - V_2 \text{ (AV)}}{KZ \text{ shunt}}$$

Where  $V_{\rm 2AV}$  is the average negative sequence voltage on the line for the minimum  $\bar{I}_2$  for fault locations F1 and F3. Z shunt is the net shunt impedance in the protected zone. The formula includes a recommended safety margin of 2.

The minimum value of keying signal for an internal fault can be obtained by taking the minimum value of the fault component of the keying signal,  $I_{KF}$ , and subtracting the load component of the keying signal,  $I_{KL}$ , directly from it.

$$I_{K}$$

min. =  $I_{KF}$  min. | -  $I_{KL}$  max.

$I_{K}$  min. should be compared with the setting for FDM to assess the margin of safety. Fig. 19B and 20B illustrate the minimum keying signal for fault locations F1 and F3.

#### PICKUP SETTING OF G4

This unit is non-directional and therefore must be set above the maximum through ground fault current  $(3I_0)$  for faults in either direction. For the sample calculation, the maximum through fault current is assumed for faults at  $F_1$  and  $F_3$ . However, if series capacitor compensated parallel lines exist, the maximum through fault current may occur for a fault on a parallel line after it opens at one terminal. On series capacitor compensated lines, a pickup setting equal to 200% of the maximum steady state through fault current is recommended.

Consideration must also be given to the possibility of unequal pole closing of the circuit breaker when the line is reclosed at the second terminal. The G4 element must be set above the maximum load transfer over a single phase for the system conditions obtaining at the time of reclosure.

### SAMPLE CALCULATIONS (Refer to Fig. 17)

Setting of FDH & FDL

Set FDH = 2/3 min.  $I_2 = .19 (2/3) = .127$  pu.

$$FDH = 4/3 FDL + I_{SC}$$

$$I_{SC} = \frac{V_2 \text{ AV}}{\frac{Z_{SC} (Z_{SR})}{Z_{SC} + Z_{SR}}} = \frac{V_2 - I_2 (Cx) \frac{ZL}{2}}{\frac{Z_{SC} (Z_{SR})}{Z_{SC} + Z_{SR}}}$$

$$= V_{LN} (R_0(\emptyset G)) - I_2(Cx)Z_{L/2} = 1 (.246) - (.19) (.5)$$

$$\frac{Z_{SC} (Z_{SR})}{Z_{SC} + Z_{SR}}$$

$$= .151 = .0063$$

pu.  $-24$

$$FDL = (.127 - .0063) 3/4 = .09 pu.$$

If shunt reactors not included in protected zone

$$I_{SC} = \frac{V_2 \text{ AV}}{Z_{SC}} = \frac{.151}{-6} = .025 \text{ pu}.$$

$$FDL = (.127 - .025) 3/4 = .0765 pu$$

.

### SELECTION OF K FACTOR

K=10 is required for faults F2 and F3. K=10 must therefore be used at both terminals.

### SETTING OF FDM

$$FDM = \frac{V_2(AV)}{Z \text{ shunt}} + \frac{V_1(AV)}{K Z \text{ shunt}}$$

=

$$\frac{.151}{-24}$$

+  $\frac{1-.151}{10(-24)}$  (From FDL setting calculation)

= .0063 +.0035

= .0098 pu. (Minimum)

If shunt reactors not included in protected zone

FDM =

$$\frac{V_2}{Z}$$

(AV) +  $\frac{V_1}{K}$  (AV)

=  $\frac{.151}{-6}$  +  $\frac{.849}{-60}$  = .025 + .014

= .039 pu

#### TESTING

### **GENERAL**

The SLD42D relay will generally be supplied from the factory mounted and wired in a static relay with the associated SSA, SLYL12, test panel and CS26 carrier. The AC test inputs can conveniently be supplied to the SLD Network Unit by the insertion of an XLA test plug in the TDA test receptacle on the test panel.

The Logic Unit must be energized with the regulated 17 volt DC and bias outputs of the associated SSA to operate any of the functions or obtain trip or auxiliary outputs. Be certain that the output circuit connection plugs (TDB, TDC, TDD) are removed from any circuits connected to the power system prior to making any tests on the relay. The output of the positive and negative-sequence networks can be checked from J1 and J2 respectively to reference. The output signals from the various logic functions can be measured at the various test points in Logic Unit with respect to TP1 (reference). These signals will be from +5 to +15 volts for the ON condition and less than +1 volt for the OFF condition. These signals can be checked with an oscilloscope, the test panel voltmeter, or a portable high-impedance voltmeter. When the test panel voltmeter is used, its negative terminal will normally be connected to the logic reference. Therefore, it is only necessary to connect the panel voltmeter test jack (meter positive) to the desired test point and depress the voltmeter pushbutton to obtain a test reading. A dual-trace oscilloscope with calibrated horizontal sweep, and external triggering facility is recommended for checking or adjusting the various time delay cards such as phase delay (J), trip integrator (P), etc.

Caution: It is a design characteristic of most electronic instruments that one of the signal input terminals is connected to the instrument chassis. Since the SLD reference voltage, which normally will be connected to the ground input of the instrument, is near the (+) station battery voltage level, the instrument chassis must be insulated from station ground. If the instrument power cord contains a third lead, that lead must NOT be connected to station ground.

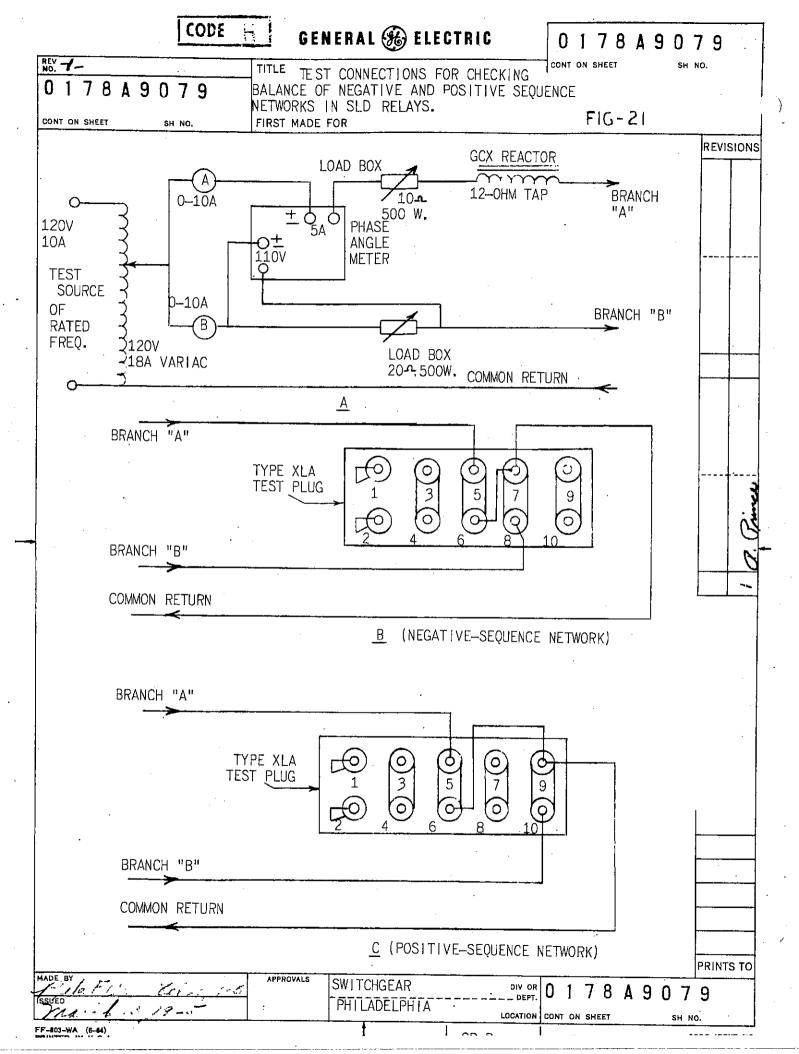

#### NETWORK BALANCE CHECK

The Network Unit circuits have been accurately preset at the factory to obtain positive-sequence cancellation in the negative-sequence network and negative-sequence cancellation in the positive-sequence network. No further adjustments should be required in the field. It is recommended, however, that the following checks be made at the time of installation to insure that nothing has occurred during shipment to upset the networks.